## INSTRUCTION MANUAL

# DECTAPE CONTROL 5552

## DECTAPE CONTROL TYPE 552 INSTRUCTION MANUAL

COPY NO.

This manual contains proprietary information. It is provided to the customers of Digital Equipment Corporation to help them properly use and maintain DEC equipment. Revealing the contents to any person or organization for any other purpose is prohibited.

#### CONTENTS

|        |                                  | Page |

|--------|----------------------------------|------|

| 1      | INTRODUCTION                     | 1-1  |

| 1-1    | General Description              | 1-1  |

| 1-2    | Type 552 Characteristics         | 1-1  |

| 1-2.1  | Physical Details                 | 1-4  |

| 1-2.2  | Electrical Details               | 1-4  |

| 1-3    | Scope of Manual                  | 1-5  |

| 1-4    | Pertinent Documents              | 1-6  |

| 1-4.1  | Manuals                          | 1-6  |

| 1-4.2  | Engineering Drawings             | 1-6  |

| 1-4.3  | Replacement Schematics           | 1-7  |

| 2      | PRINCIPLES OF OPERATION          | 2-1  |

| 2-1    | DECtape Format                   | 2-1  |

| 2-1.1  | Mark-Channel Format              | 2-3  |

| 2-2    | DECtape Instructions             | 2-4  |

| 2-3    | Control Modes                    | 2-5  |

| 2-4    | Functional Description           | 2-7  |

| 2-4.1  | Data Buffer (DB)                 | 2-7  |

| 2-4.2  | Read/Write Buffer (R/WB)         | 2-8  |

| 2-4.3  | Write Register                   | 2-8  |

| 2-4.4  | Read Register                    | 2-8  |

| 2-4.5  | Device Selector (DS)             | 2-8  |

| 2-4.6  | Select Register                  | 2-8  |

| 2-4.7  | Decoder                          | 2-9  |

| 2-4.8  | Motion Register                  | 2-9  |

| 2-4.9  | Status Register                  | 2-9  |

| 2-4.10 | Function Register                | 2-10 |

| 2-4.11 | Memory Address Counter (MAC)     | 2-10 |

| 2-4.12 | Window (W)                       | 2-10 |

| 2-4.13 | Longitudinal Parity Buffer (LPB) | 2-11 |

| 2-4.14 | Error Flag                       | 2-11 |

| 2-4.15 | DECtape Flag (DT)                | 2-12 |

| 2-4.16 | Data Flag                        | 2-12 |

#### CONTENTS (continued)

|       |                                   | Page |

|-------|-----------------------------------|------|

| 2-5   | Programmed Operation              | 2-13 |

| 2-6   | Available Software                | 2-14 |

| 3     | CONTROL LOGIC                     | 3-1  |

| 3-1   | Introduction                      | 3-1  |

| 3-2   | Computer Interface                | 3-1  |

| 3-2.1 | In/Out Control                    | 3-2  |

| 3-2.2 | Data Transfers                    | 3-6  |

| 3-3   | Read/Write Logic                  | 3-6  |

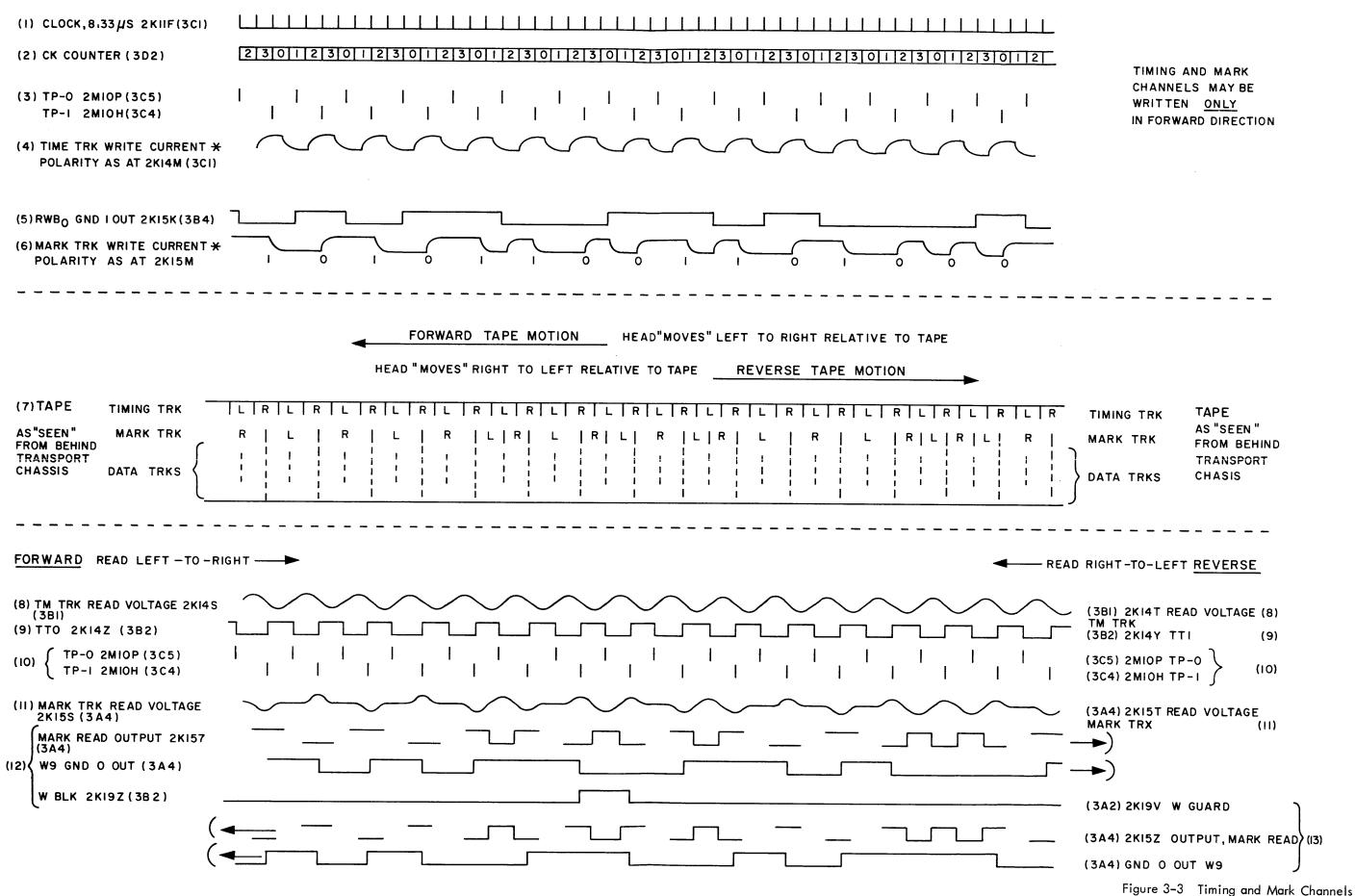

| 3-4   | Timing and Mark Channels          | 3-10 |

| 3-5   | All-Bits Mode                     | 3-12 |

| 3-5.1 | Control Pulses and Data Transfers | 3-12 |

| 3-5.2 | Tape Operations                   | 3-15 |

| 3-6   | Search and Data Modes             | 3-21 |

| 3-6.1 | Control States                    | 3-21 |

| 3-6.2 | Search                            | 3-22 |

| 3-6.3 | Write Data                        | 3-25 |

| 3-6.4 | Read Data                         | 3-29 |

| 3-6.5 | Read/Write Function Switching     | 3-30 |

| 4     | CIRCUIT DESCRIPTION               | 4-1  |

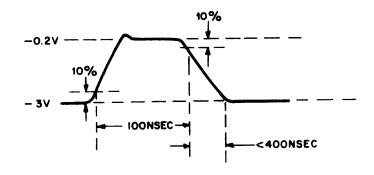

| 4-1   | Introduction                      | 4-1  |

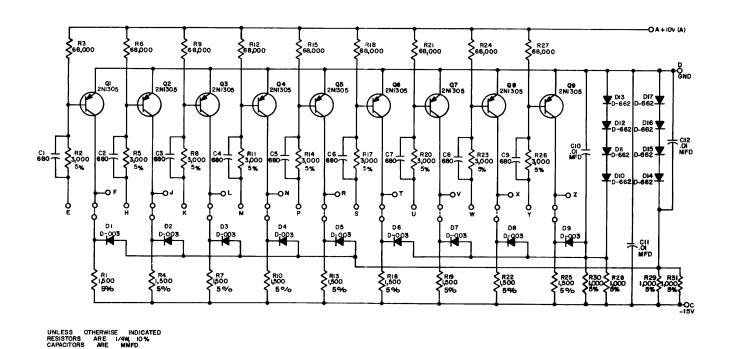

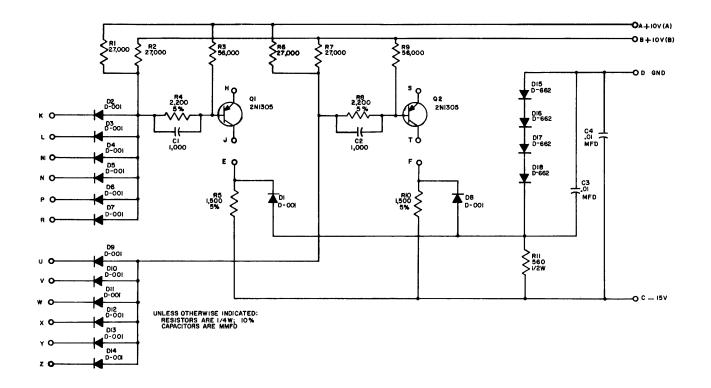

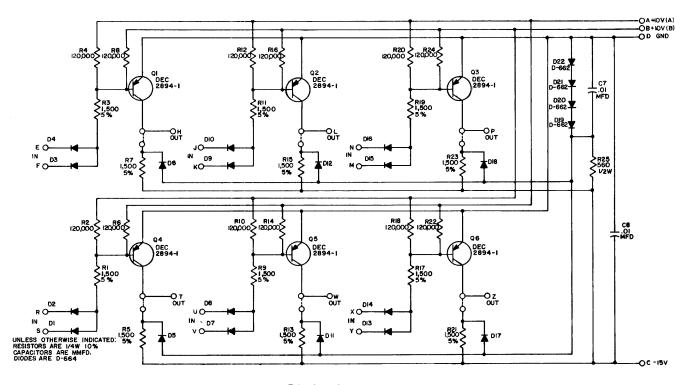

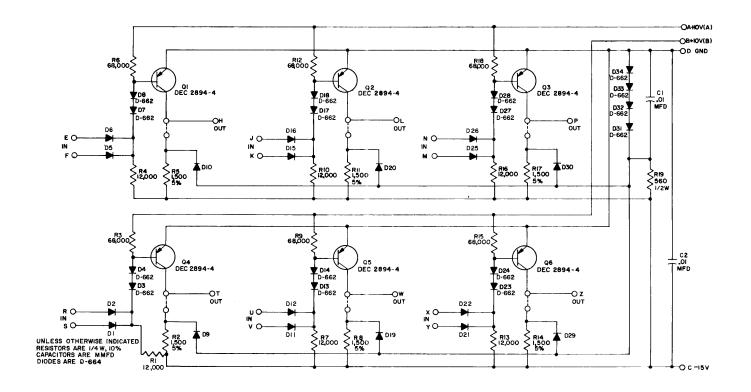

| 4-2   | Conventional Circuits             | 4-1  |

| 4-2.1 | Clamped Loads                     | 4-1  |

| 4-2.2 | Inverter                          | 4-2  |

| 4-2.3 | Gates                             | 4-2  |

| 4-2.4 | Capacitor-Diode (C-D) Gates       | 4-3  |

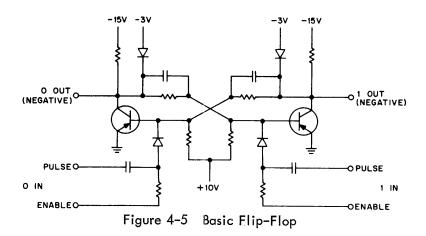

| 4-2.5 | Flip-Flops                        | 4-4  |

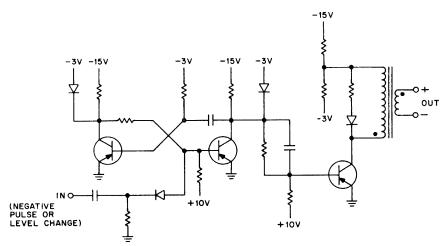

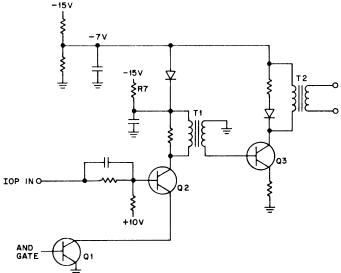

| 4-2.6 | Pulse Amplifiers                  | 4-5  |

| 4-3   | Special Circuits                  | 4-7  |

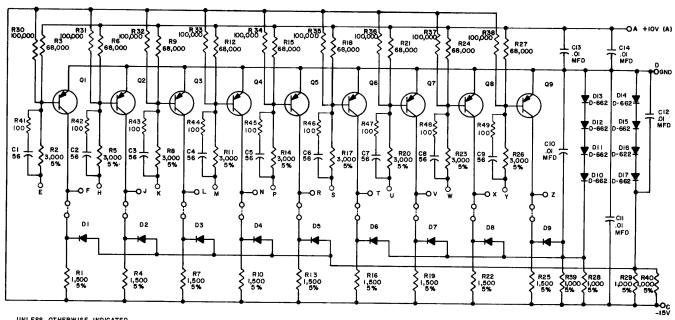

| 4-3.1 | Level Standardizer Type 1501      | 4-7  |

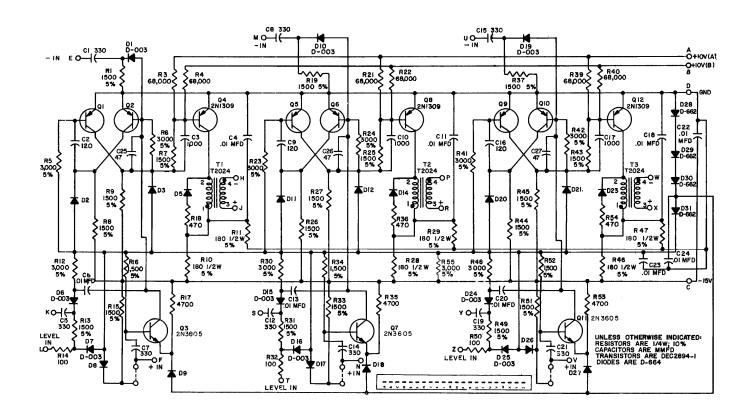

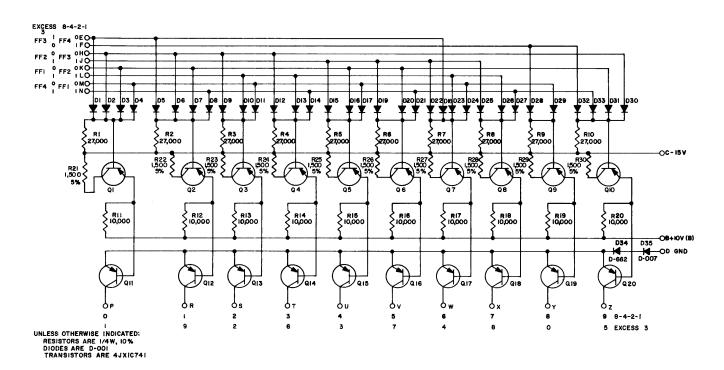

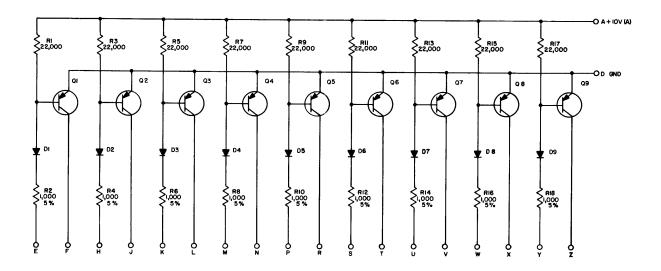

| 4-3.2 | BCD Light Driver Type 4671        | 4-8  |

| 4-3.3 | Integrating Delay Type 4303       | 4-8  |

#### CONTENTS (continued)

|              |                                              | Page         |

|--------------|----------------------------------------------|--------------|

| 4-3.4        | Clock Type 4401                              | 4-10         |

| 4-3.5        | Mark Track Decoder Type 4260                 | 4-11         |

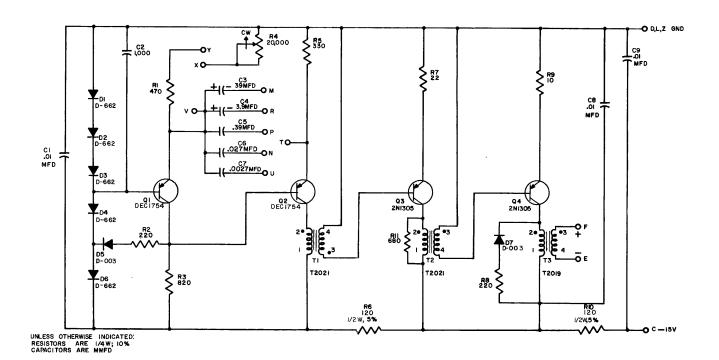

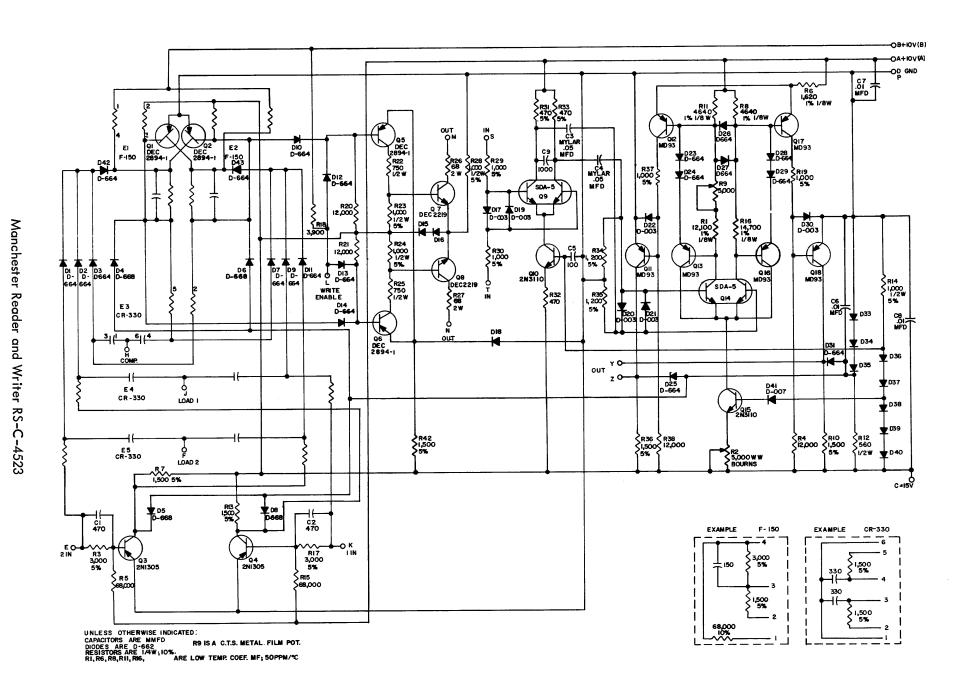

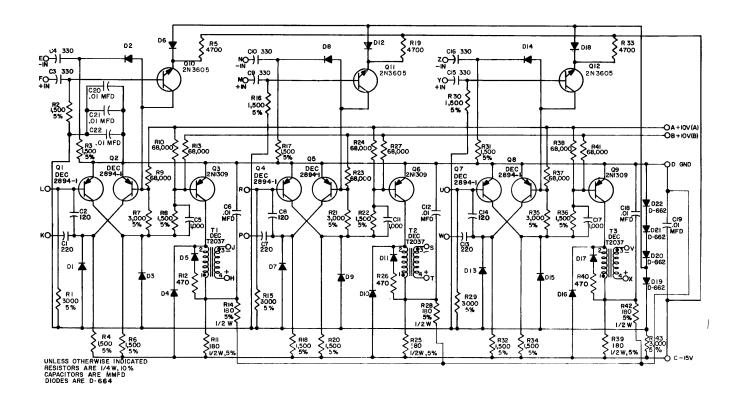

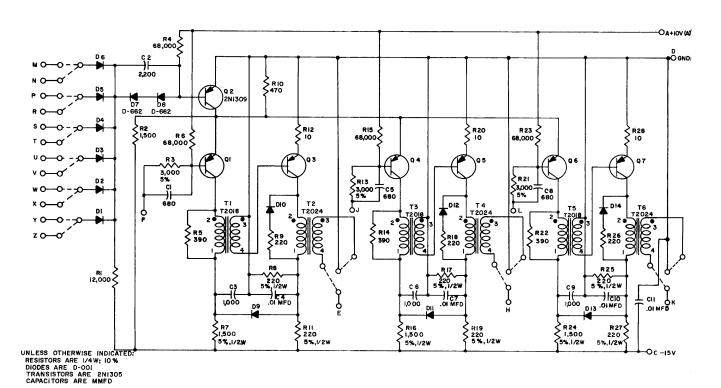

| 4-3.6        | Manchester Reader and Writer Type 4523       | 4-13         |

| 5            | MAINTENANCE                                  | 5-1          |

| 5-1          | Introduction                                 | 5 <b>-</b> 1 |

| 5-2          | Wiring                                       | 5-2          |

| 5-2.1        | Interface                                    | 5-2          |

| 5-2.2        | Module Location                              | 5 <b>-</b> 2 |

| 5-2.3        | Wiring List                                  | 5-2          |

| 5 <b>-</b> 3 | Module Handling                              | 5-2          |

| 5-3.1        | Module Removal                               | 5-2          |

| 5-3.2        | Module Replacement                           | 5 <b>-</b> 3 |

| 5-4          | Preventive Maintenance                       | 5-4          |

| 5-4.1        | Type 728 Power Supply Check                  | 5-5          |

| 5-4.2        | Type 4303 Delay Check                        | 5 <b>-</b> 5 |

| 5-4.3        | Type 4306 Delay Check                        | 5-5          |

| 5-4.4        | Type 4401 Variable Clock Check               | 5-7          |

| 5-4.5        | Type 4523 Manchester Reader and Writer Check | 5 <b>-</b> 7 |

| 5-4.6        | Read/Write Circuit Checks                    | 5-9          |

| 5 <b>-</b> 5 | Marginal Checks                              | 5-9          |

| 5-6          | Corrective Maintenance                       | 5-12         |

| 5 <b>-7</b>  | Spare Parts                                  | 5-12         |

| 6            | ENGINEERING DRAWINGS                         | 6-1          |

| 6-1          | Introduction                                 | 6-1          |

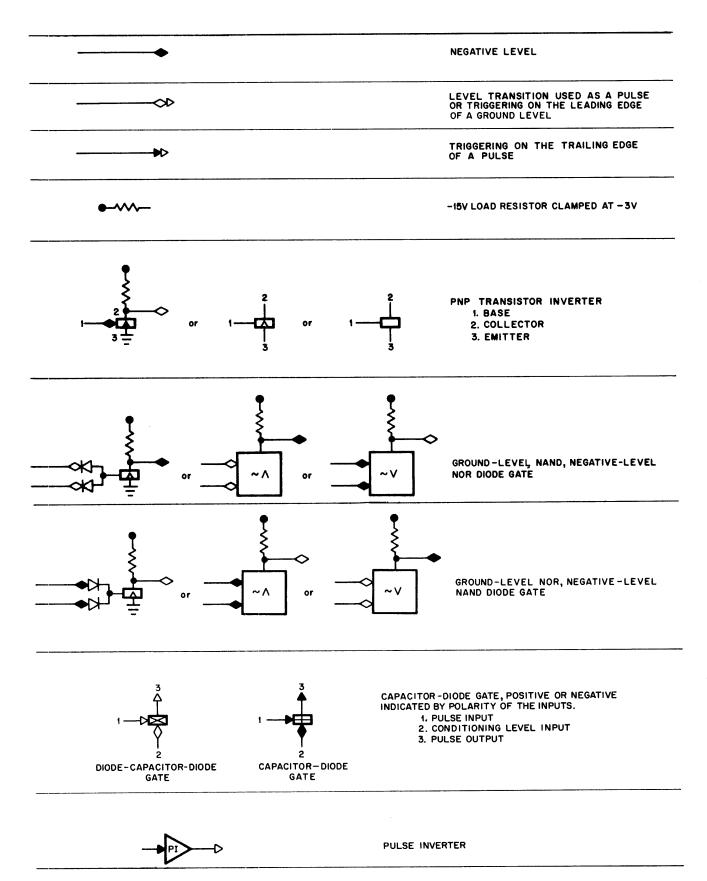

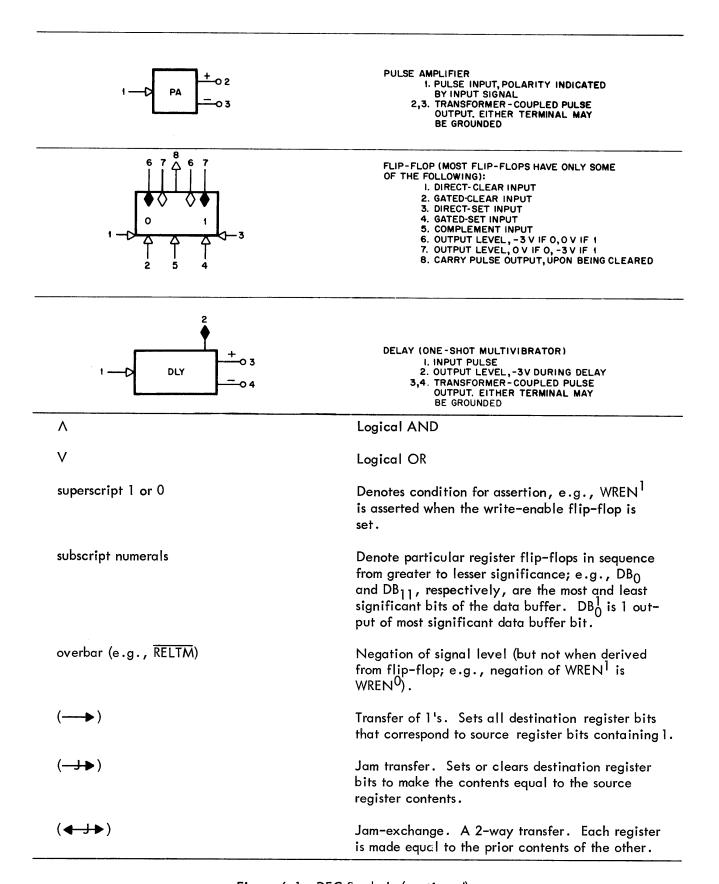

| 6-2          | Circuit Symbols                              | 6-1          |

| 6-2.1        | Logic Signal Symbols                         | 6-1          |

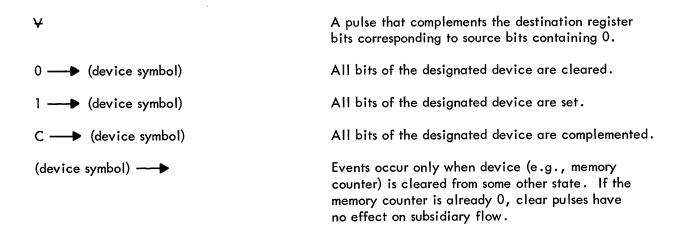

| 6-2.2        | Logic Levels                                 | 6-4          |

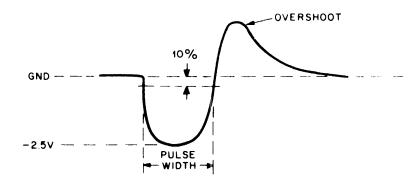

| 6-2.3        | FLIP CHIP Pulses                             | 6-4          |

| 6-3          | DEC Engineering Drawing Conventions          | 6-5          |

| 6-4          | Replacement Schematics                       | 6-5          |

#### CONTENTS (continued)

#### ILLUSTRATIONS

| Figure |                                                                                         | Page         |  |

|--------|-----------------------------------------------------------------------------------------|--------------|--|

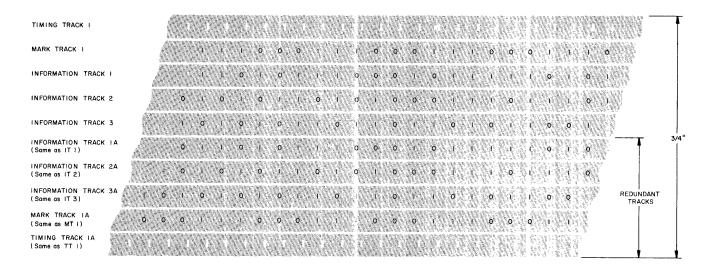

| 21     | DECtape Track Allocation Showing Redundantly Paired Tracks                              | 2-1          |  |

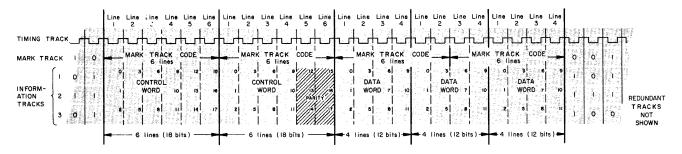

| 22     | Basic Six Line DECtape Unit                                                             | 2-2          |  |

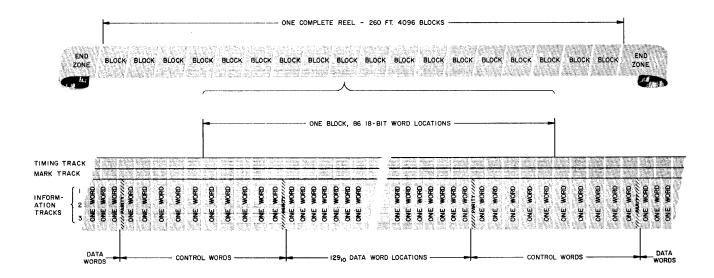

| 2-3    | DECtape Control and Data Word Assignments                                               |              |  |

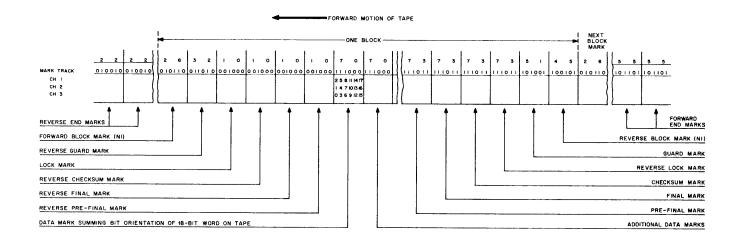

| 24     | DECtape Mark Track Format (Assumes 256 <sub>10</sub> Data Words Per Block)              | 2-3          |  |

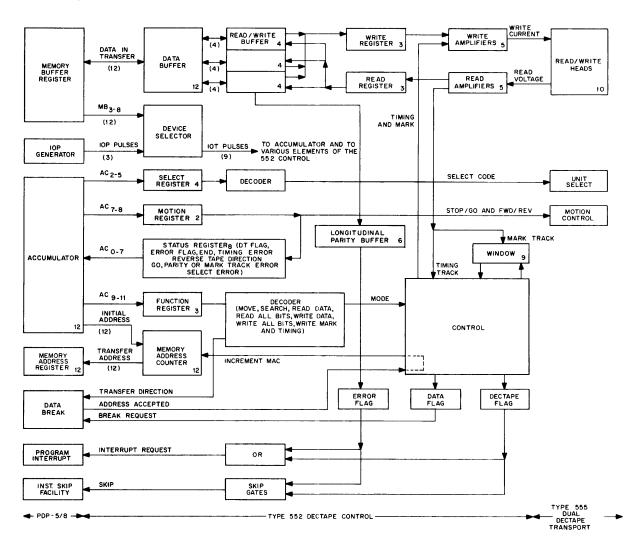

| 25     | Block Diagram of Type 552 DECtape Control Plus PDP-5/8 and Transport Interface Elements | 2-7          |  |

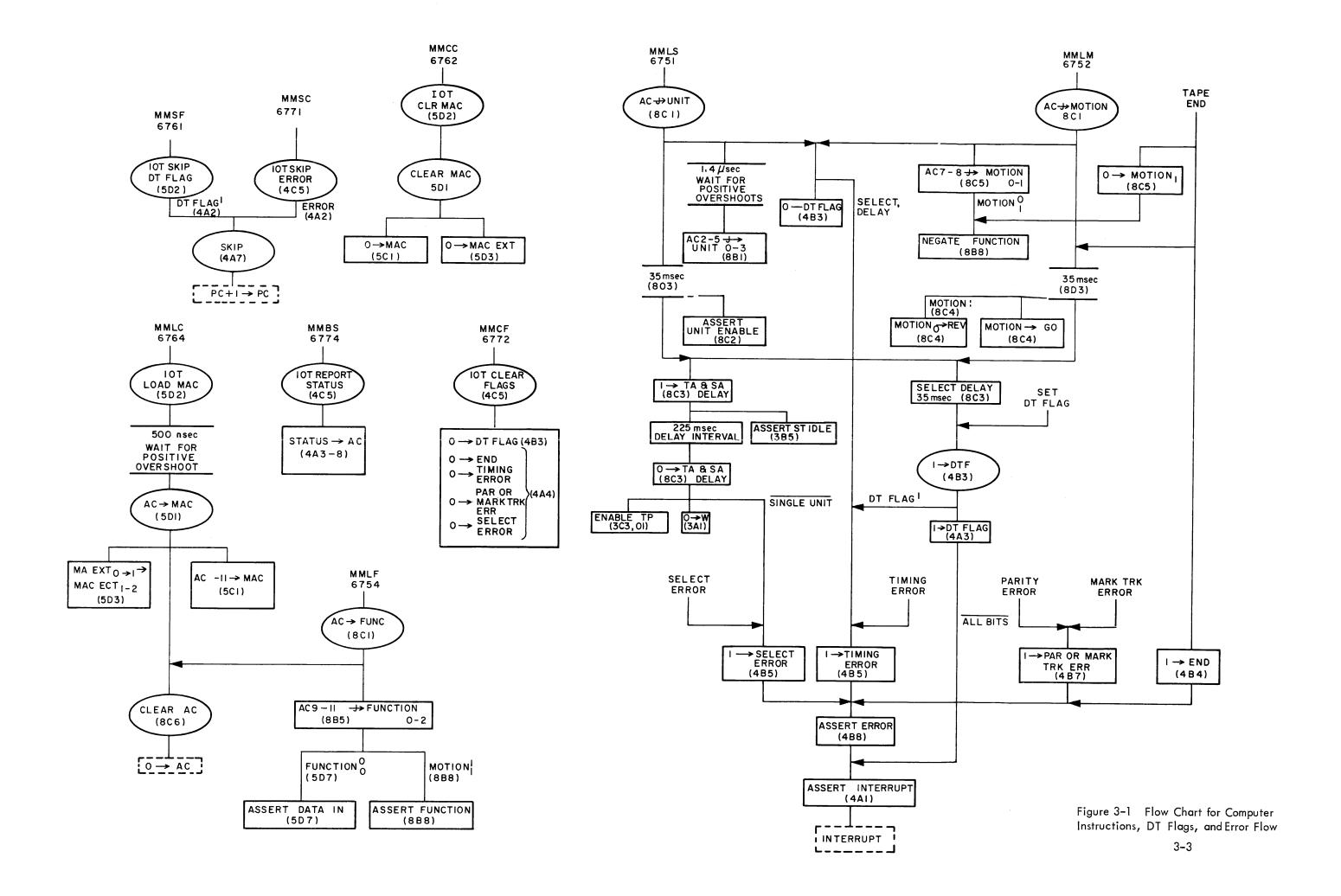

| 31     | Flow Chart for Computer Instructions, DT Flags, and Error Flow                          | 3-3          |  |

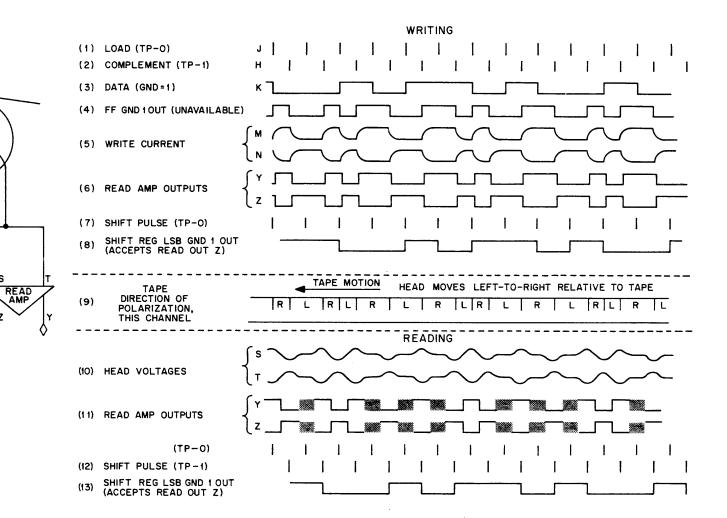

| 32     | Read/Write Waveforms                                                                    | 3-7          |  |

| 33     | Timing and Mark Channels                                                                | 3-13         |  |

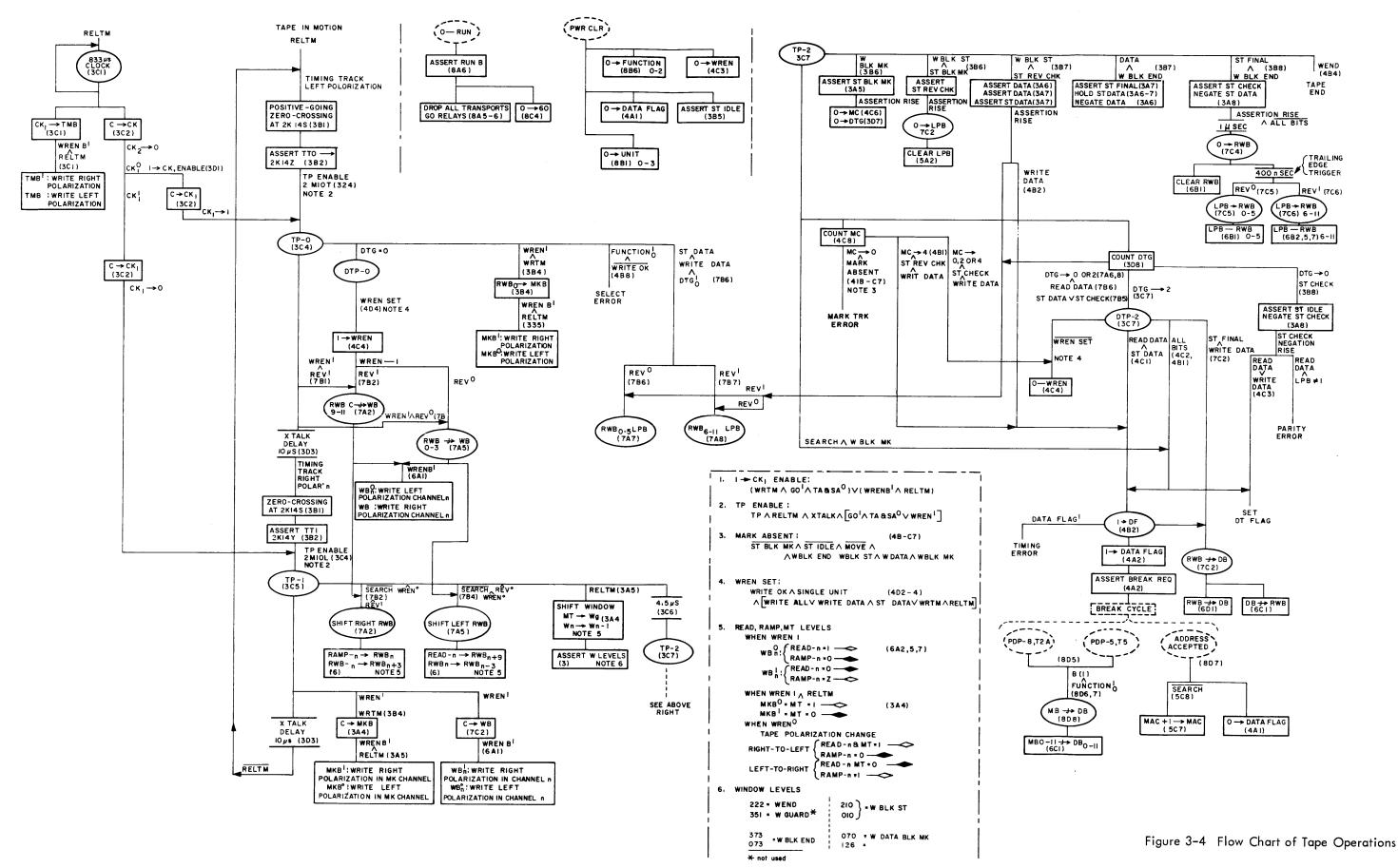

| 34     | Flow Chart of Tape Operations                                                           | 3-1 <i>7</i> |  |

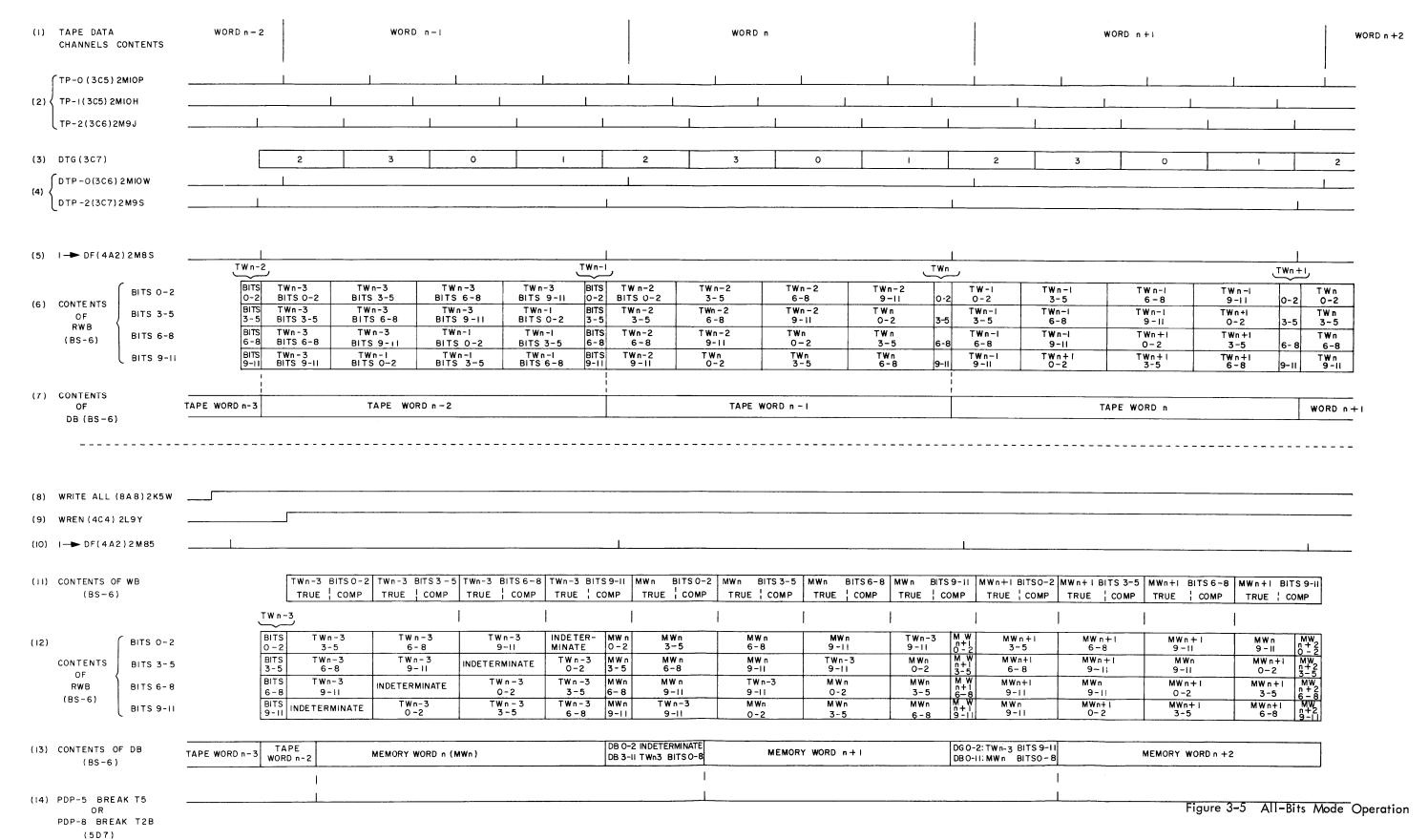

| 3-5    | All-Bits Mode Operation                                                                 | 3-19         |  |

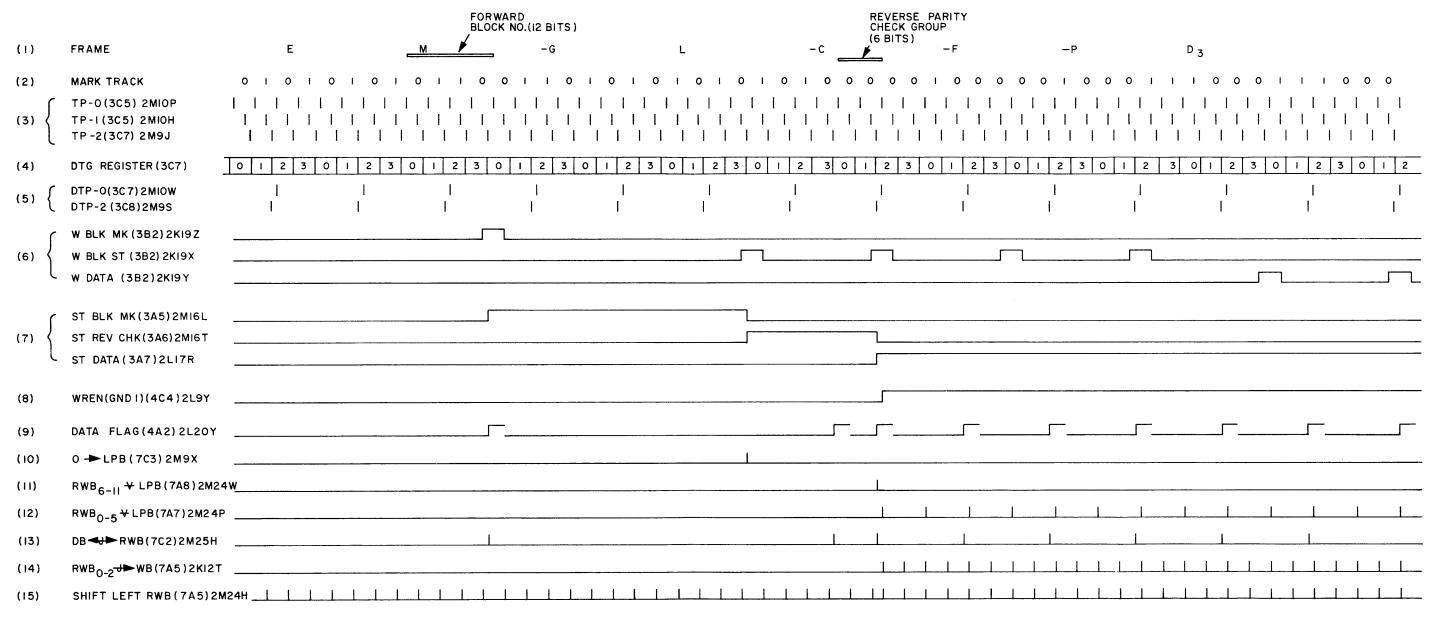

| 36     | Search and Data Mode Timing Block Start                                                 | 3-23         |  |

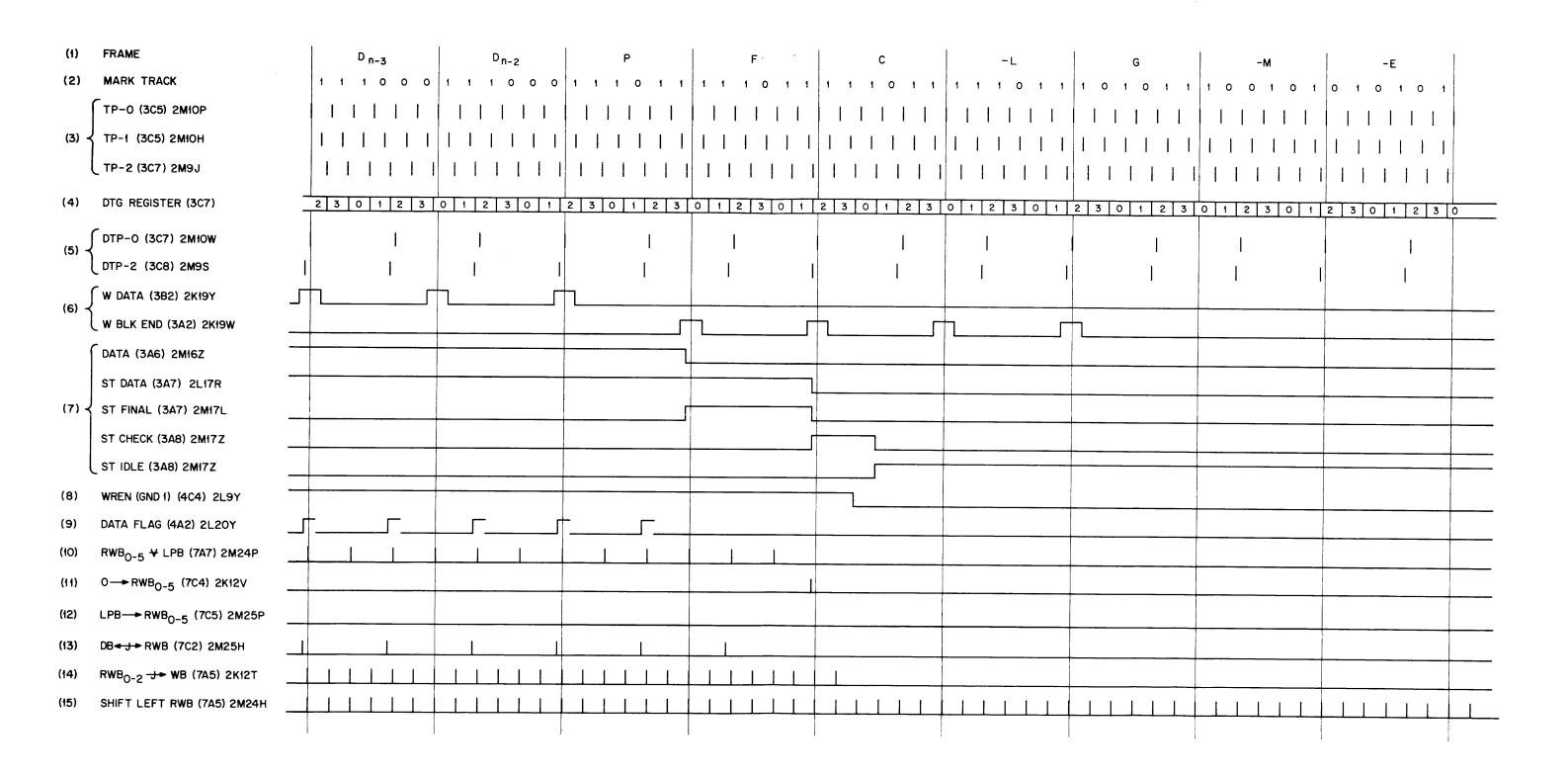

| 3-7    | Data Mode Timing                                                                        | 3-27         |  |

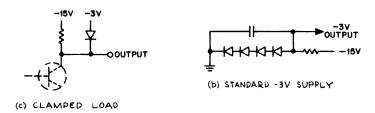

| 4-1    | Clamped Load and Standard Power Supply                                                  | 4-2          |  |

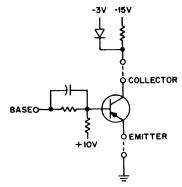

| 4-2    | Basic Inverter                                                                          | 4-2          |  |

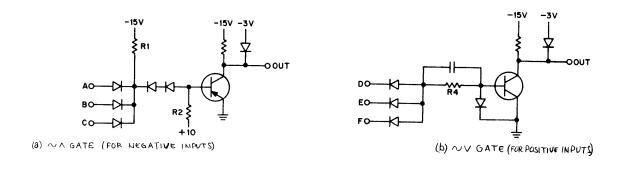

| 43     | NAND Gates                                                                              | 4-3          |  |

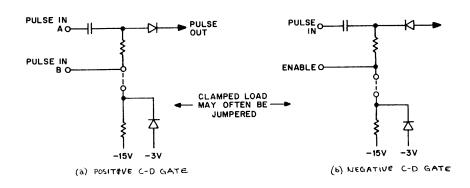

| 4-4    | Capacitor-Diode (C-D) Gates                                                             | 4-4          |  |

| 45     | Basic Flip-Flops                                                                        | 4-5          |  |

| 46     | Basic MV-Type Pulse Amplifier                                                           | 4-6          |  |

| 47     | Basic Transformer-Coupled Pulse Amplifier                                               | 4-6          |  |

| 5-1    | Read/Write Waveforms of Type 4523 Manchester Reader and Writer                          | 5-10         |  |

| 61     | DEC Symbols                                                                             | 6-1          |  |

| 62     | FLIP CHIP R-Series Pulse                                                                | 6-4          |  |

| 6-3    | FLIP CHIP B-Series Pulse                                                                | 6-5          |  |

|        | TABLES                                                                                  |              |  |

| Table  |                                                                                         |              |  |

| 1-1    | Summary of Equipment Characteristics for the Type 552 DECtape Control                   | 1-1          |  |

| 2-1    | DECtape Instruction List                                                                | 2-4          |  |

| 2-2    | Significance of Accumulator Bits 0-7                                                    | 2-9          |  |

#### TABLES (continued)

| <u>Table</u>       |                                                           | Page |

|--------------------|-----------------------------------------------------------|------|

| 4-1                | Decoder Outputs for Mark Track Decoder Type 4260          | 4-12 |

| 5-1                | Recommended Maintenance Equipment                         | 5-1  |

|                    |                                                           |      |

|                    | ENGINEERING DRAWINGS                                      |      |

| Drawing            |                                                           |      |

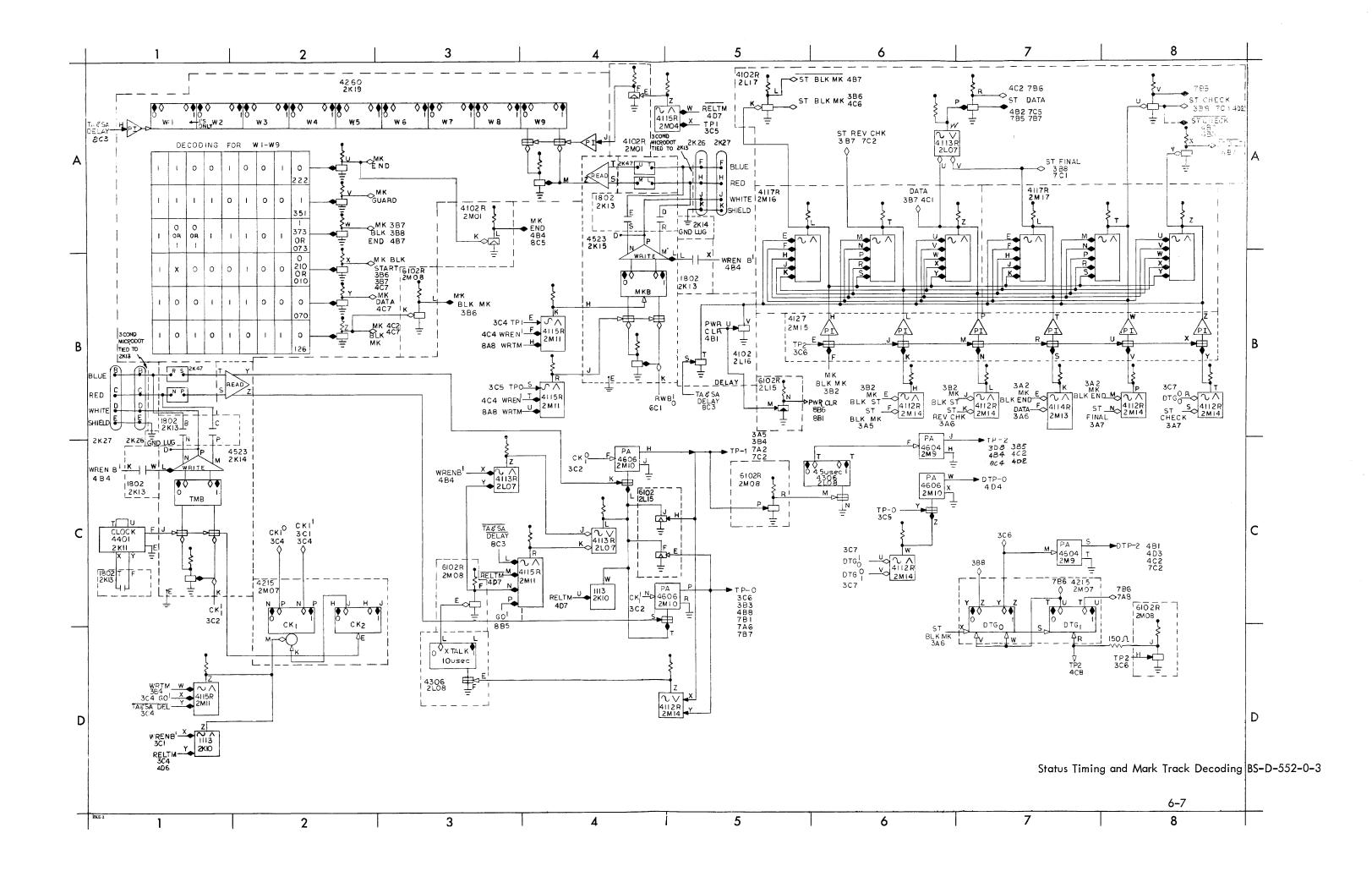

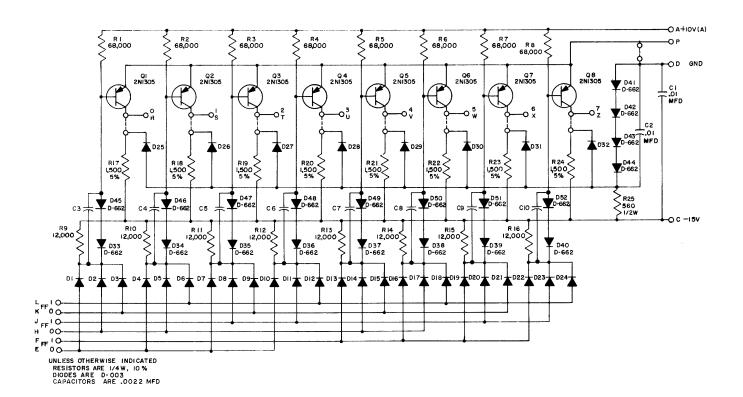

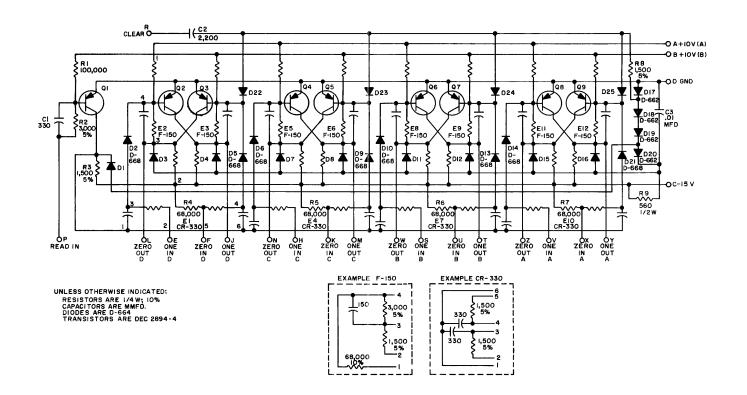

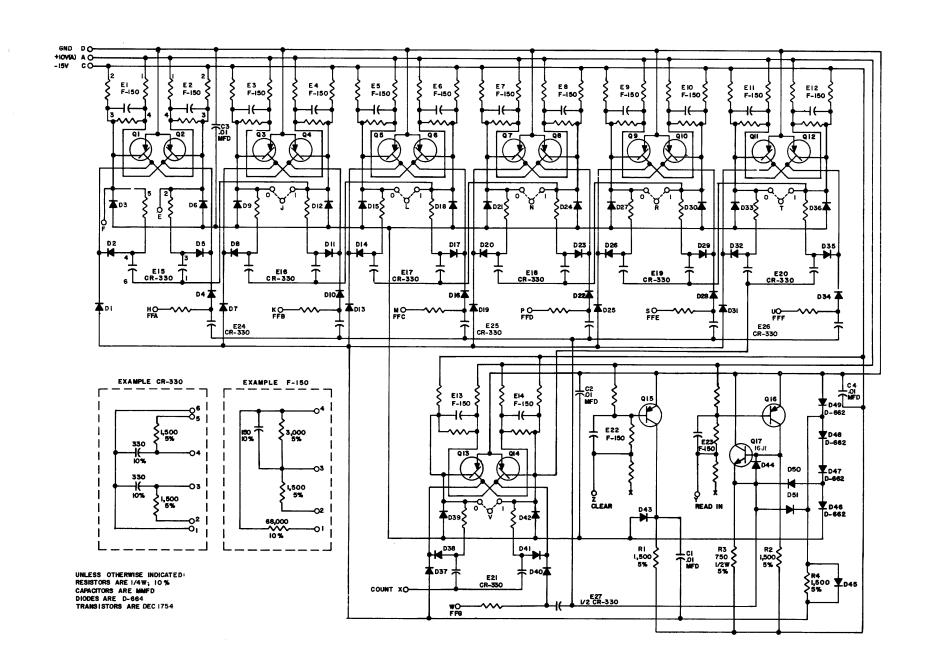

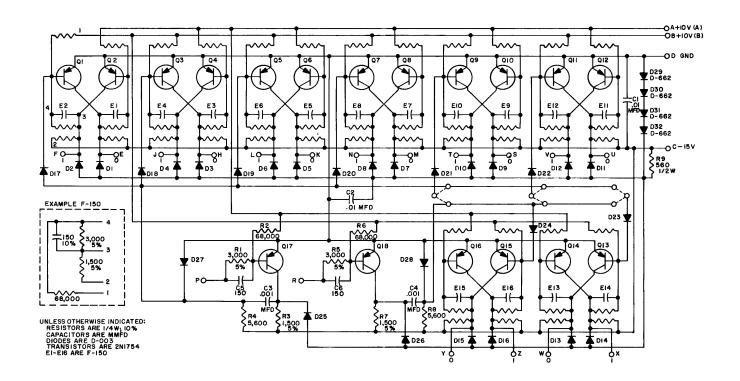

| BS-D-552-0-3       | Status Timing and Mark Track Decoding                     | 6-7  |

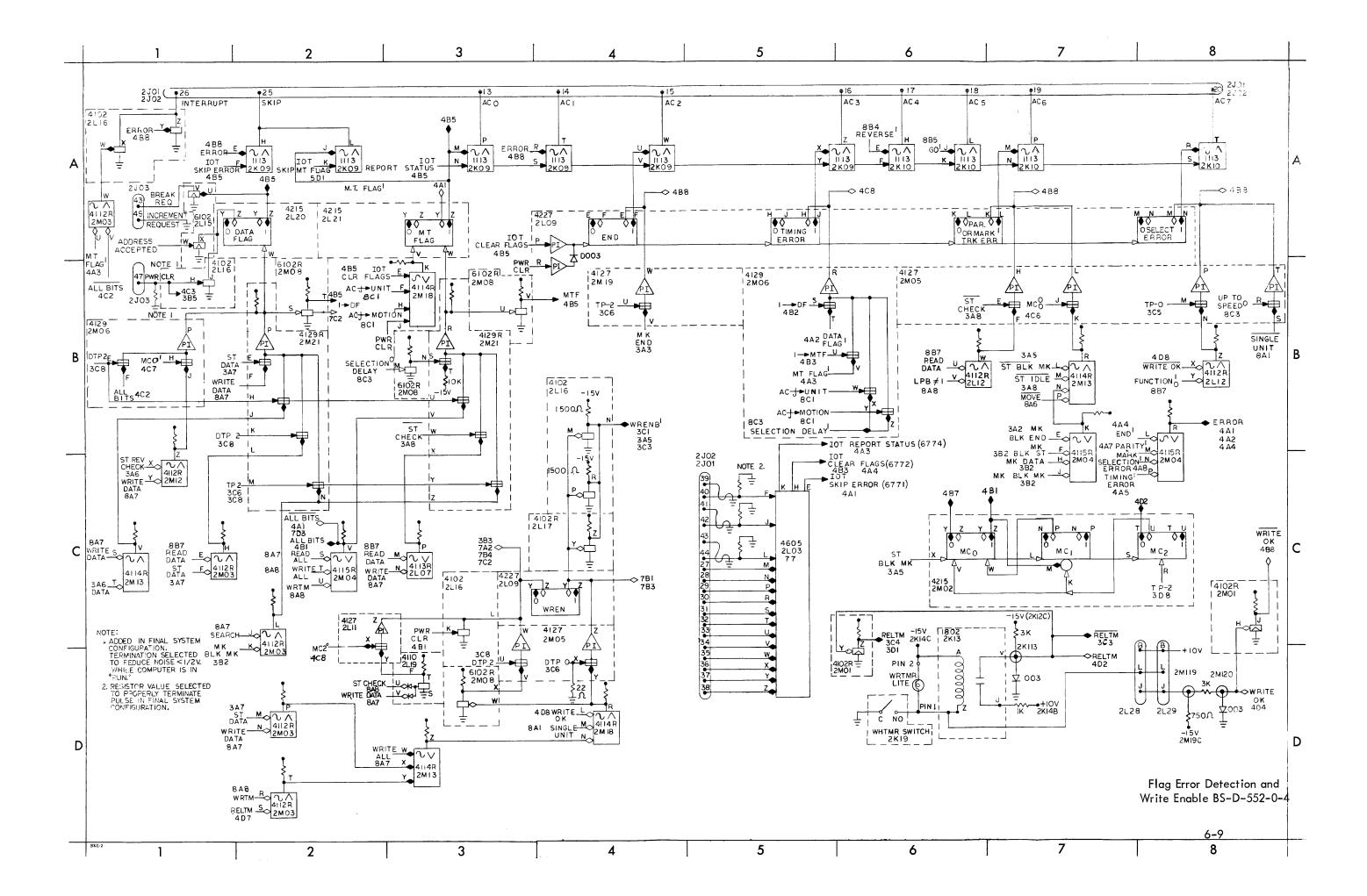

| BS-D-552-0-4       | Flag Error Detection and Write Enable                     | 6-9  |

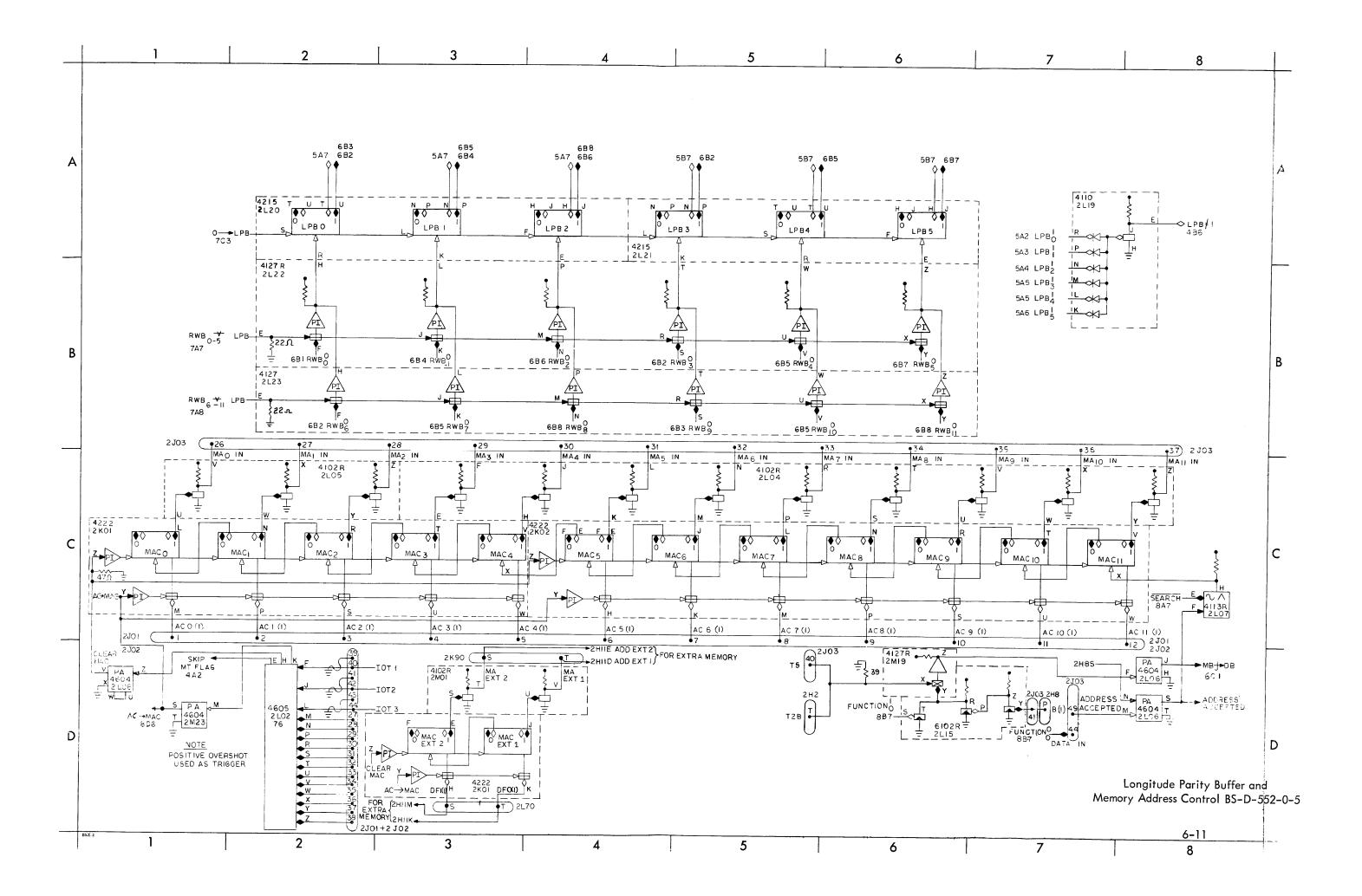

| BS-D-552-0-5       | Longitude Parity Buffer and Memory Address Control        | 6-11 |

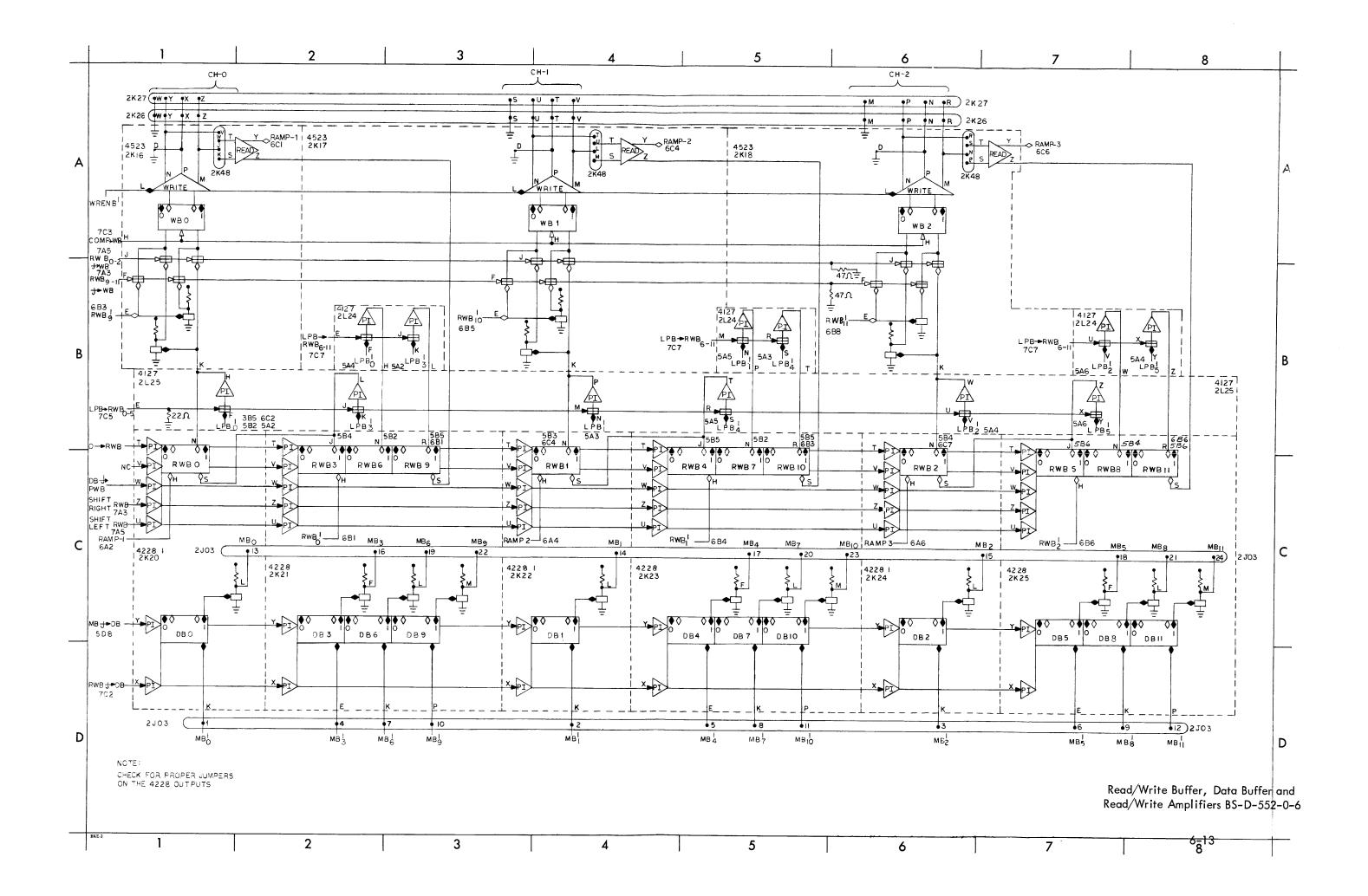

| BS-D-552-0-6       | Read/Write Buffer, Data Buffer, and Read/Write Amplifiers | 6-13 |

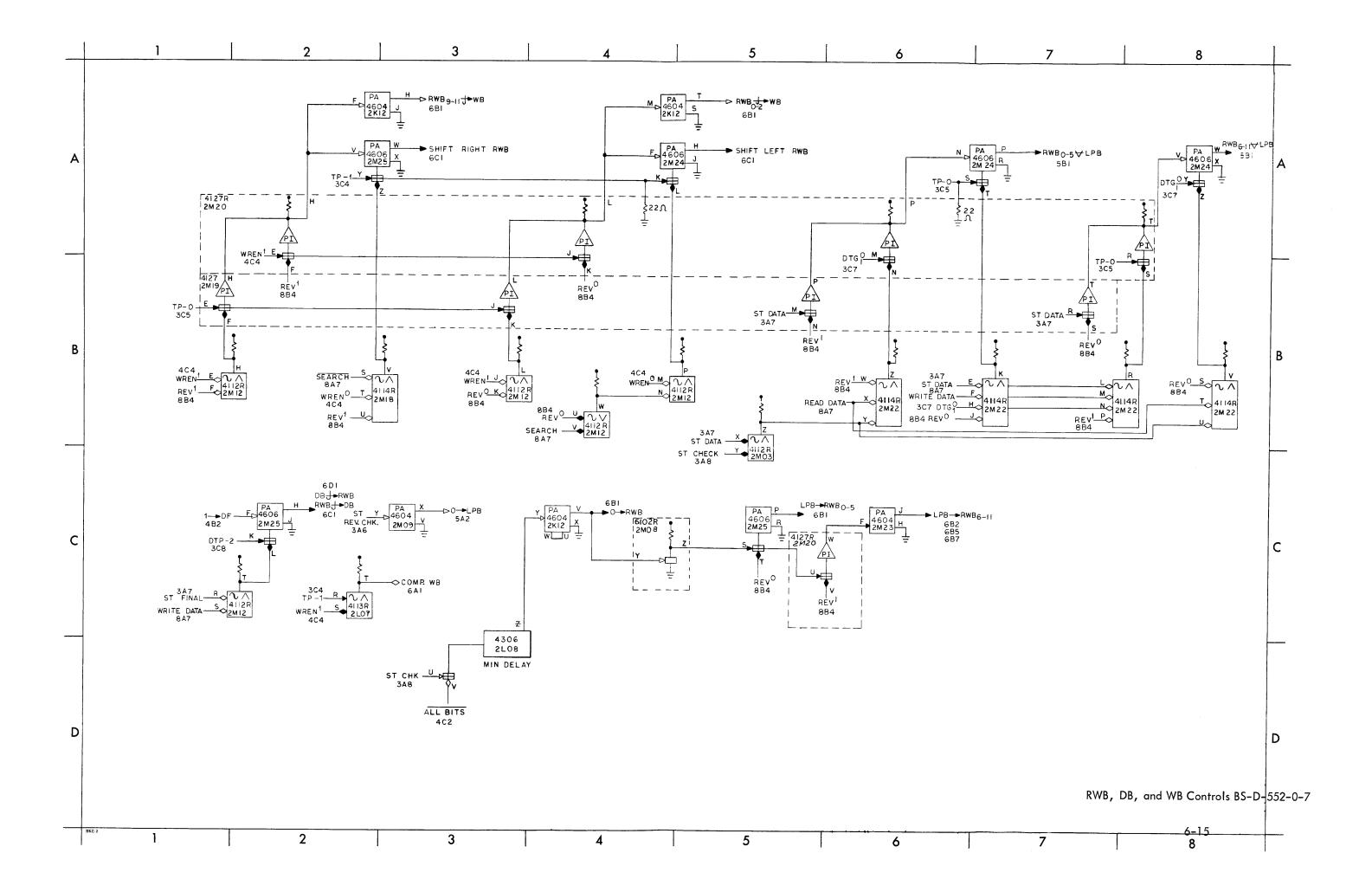

| BS-D-552-0-7       | RWB, DB, and WB Controls                                  | 6-15 |

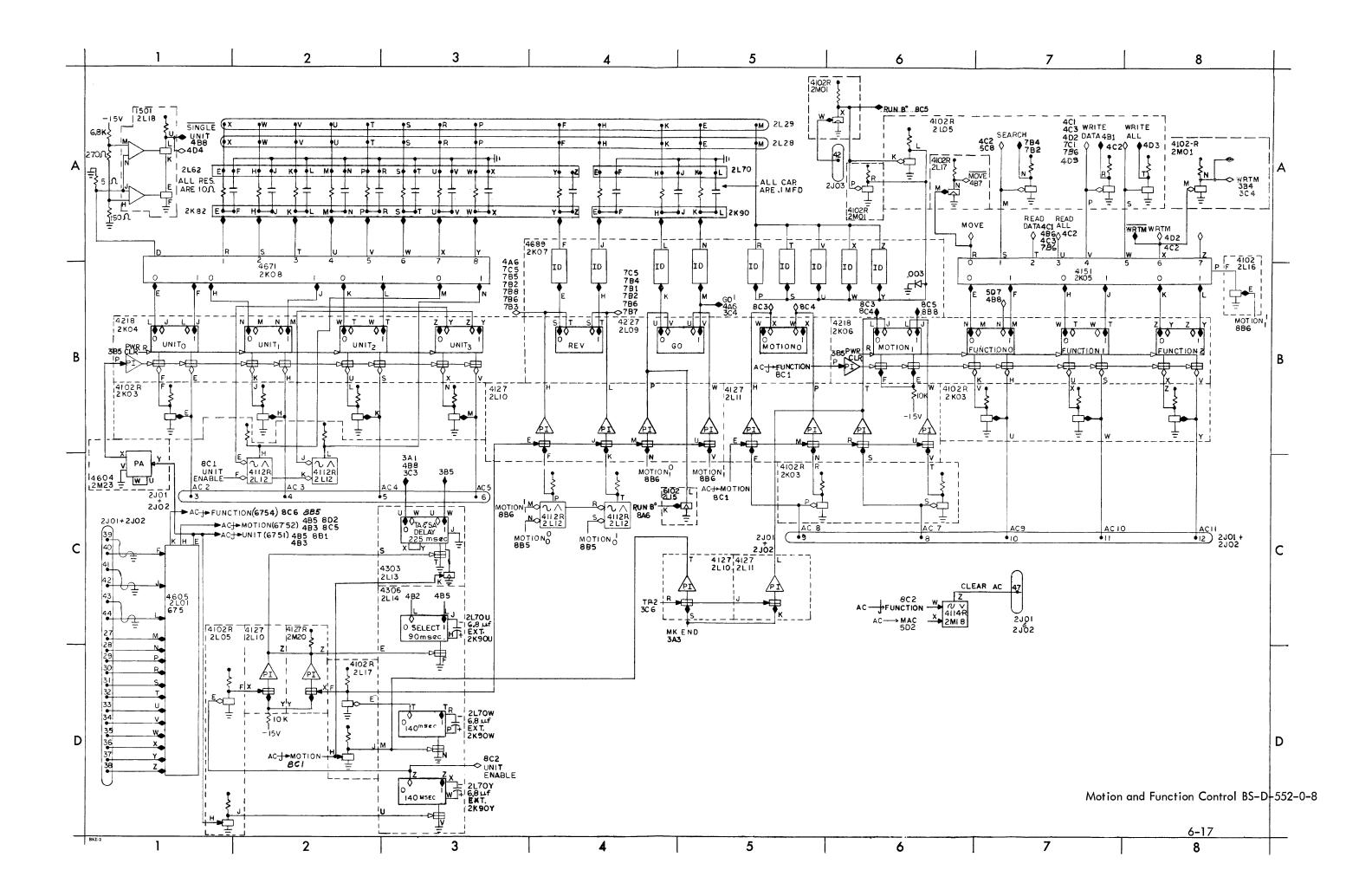

| BS-D-552-0-8       | Motion and Function Control                               | 6-17 |

| UML-D-552-0-14     | Utilization Module Location                               | 6-19 |

| UML-D-552-0-18     | Utilization Module Location                               | 6-21 |

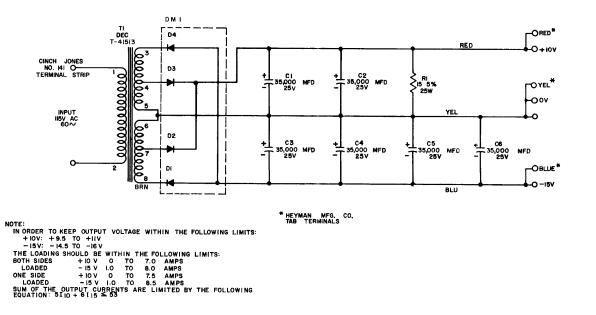

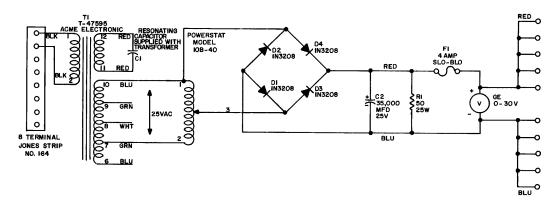

| RS-B-728           | Power Supply                                              | 6-23 |

| RS-B-734           | 20v Variable Power Supply                                 | 6-23 |

| RS-B-1113          | Diode                                                     | 6-24 |

| RS-B-1501          | Level Standardizer                                        | 6-24 |

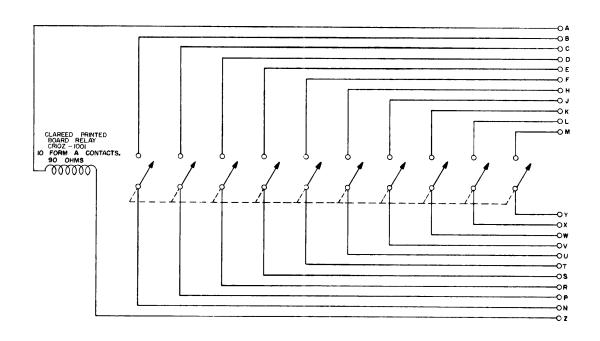

| RS-B-1802          | Relay                                                     | 6-25 |

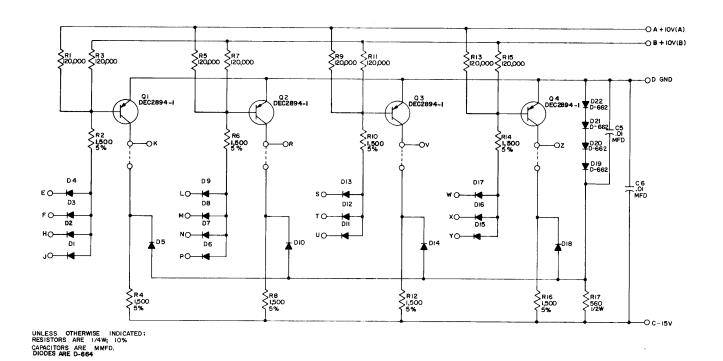

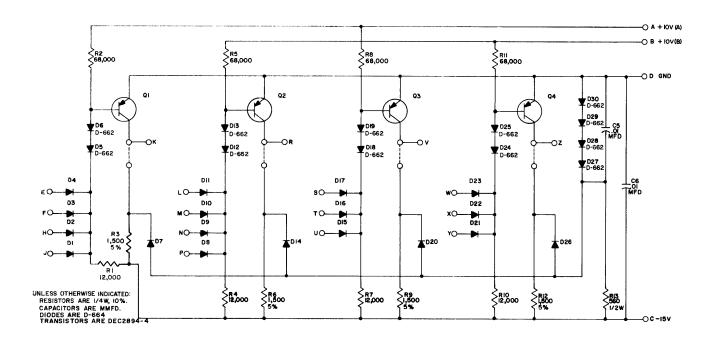

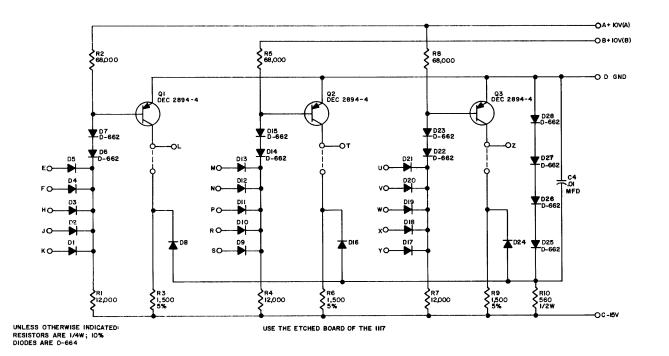

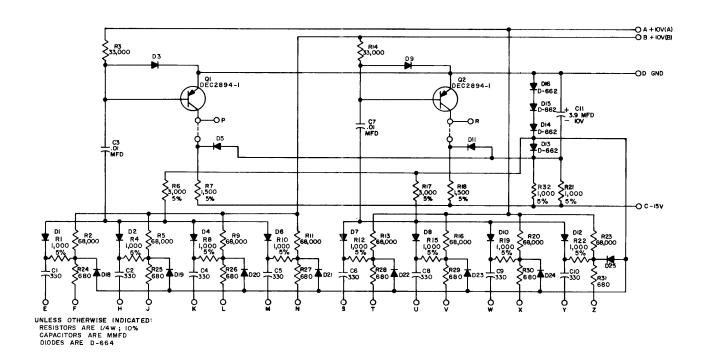

| RS-B-4102          | Inverter                                                  | 6-25 |

| RS-B-4110          | Diode Unit                                                | 6-26 |

| RS-B-4112          | Diode                                                     | 6-26 |

| RS-B-4113          | Diode                                                     | 6-27 |

| RS-B-4114          | Diode                                                     | 6-27 |

| RS-B-4115          | Diode                                                     | 6-28 |

| RS-B-4117          | Diode                                                     | 6-28 |

| RS-B-4127          | Capacitor Diode Inverter                                  | 6-29 |

| RS-B-4129          | Capacitor Diode Inverter                                  | 6-29 |

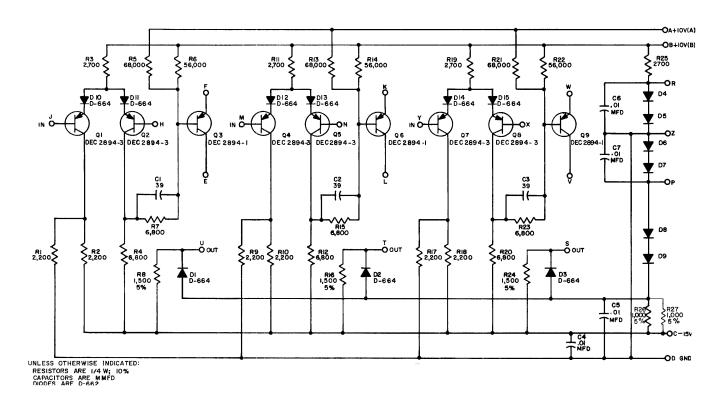

| RS-B-41 <i>5</i> 1 | Binary-to-Octal Decoder                                   | 6-30 |

| RS-B-4215          | 4-Bit Counter                                             | 6-30 |

| RS-B-4218          | Quadruple Flip-Flop                                       | 6-31 |

| RS-C-4222          | 7-Bit Counter with Readin Gates                           | 6-32 |

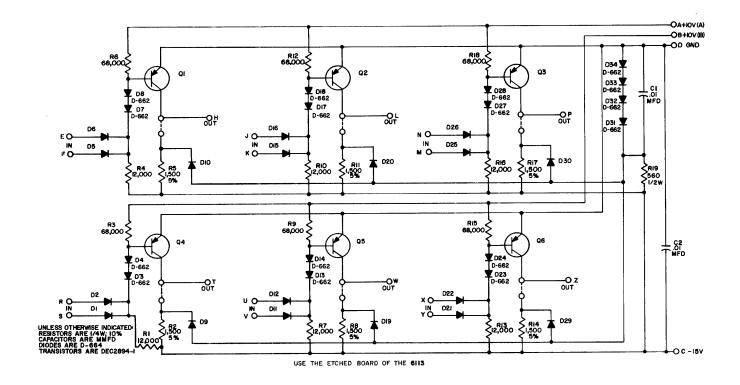

| RS-B-4227          | 8 Unbuffered Flip-Flops                                   | 6-33 |

|                    |                                                           | _    |

#### ENGINEERING DRAWINGS (continued)

| Drawing   |                                           | <u>Page</u> |

|-----------|-------------------------------------------|-------------|

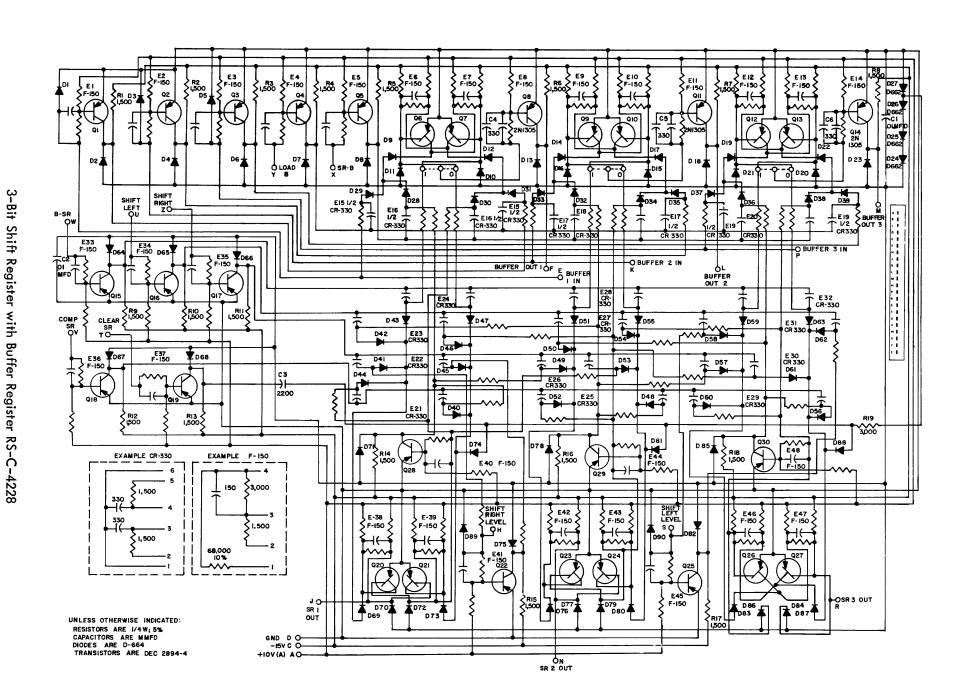

| RS-C-4228 | 3-Bit Shift Register with Buffer Register | 6-34        |

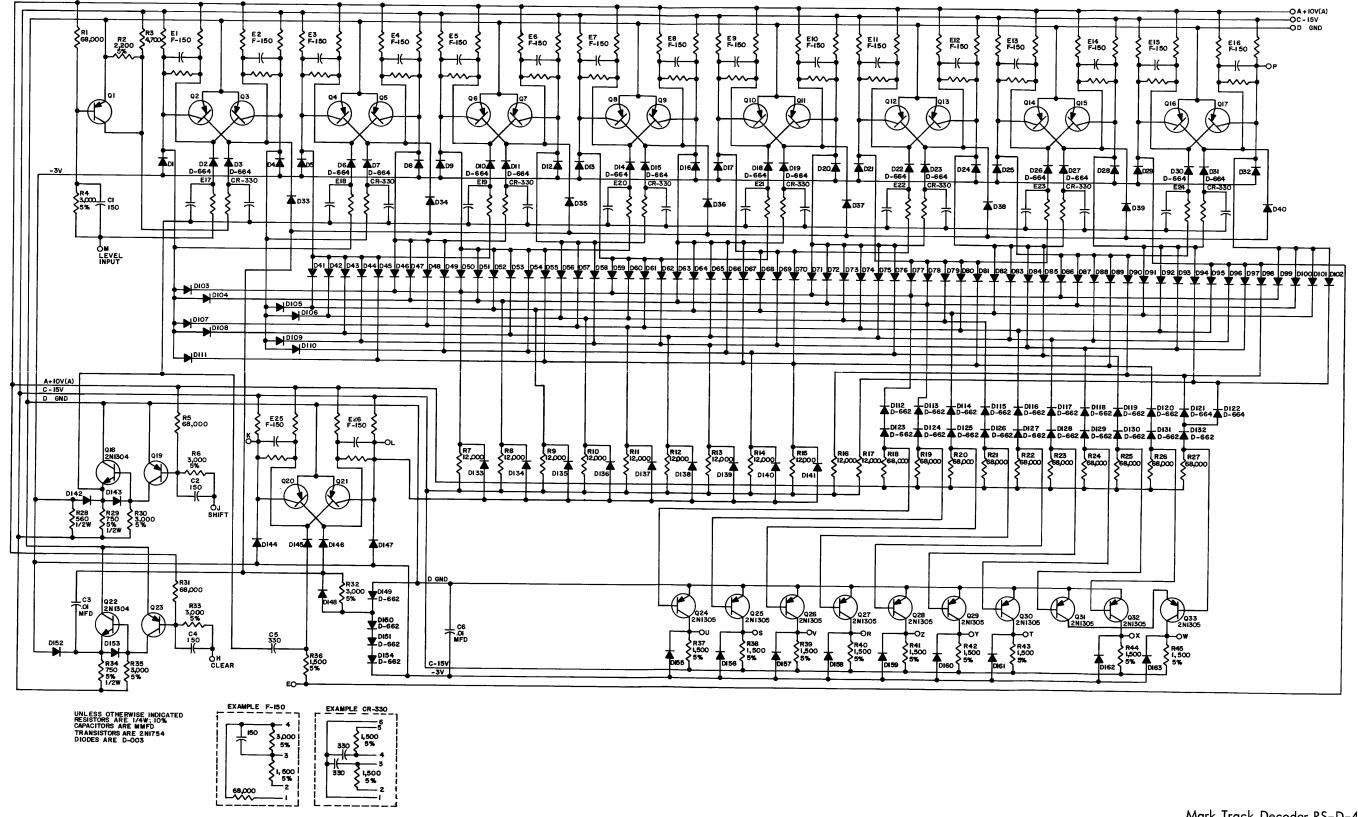

| RS-D-4260 | Mark Track Decoder                        | 6-35        |

| RS-B-4303 | Integrating One-Shot                      | 6-37        |

| RS-C-4306 | Delay                                     | 6-38        |

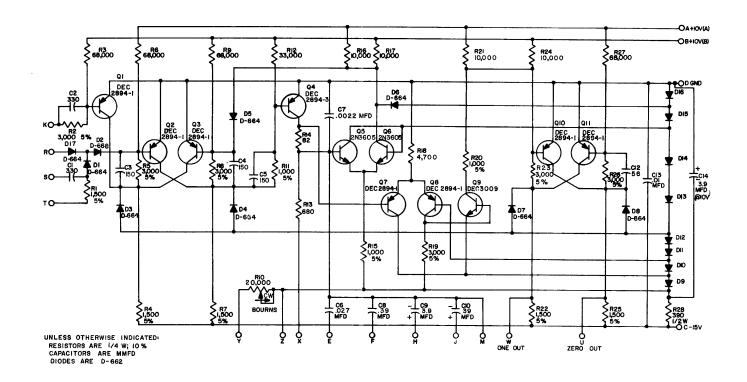

| RS-B-4401 | Clock                                     | 6-39        |

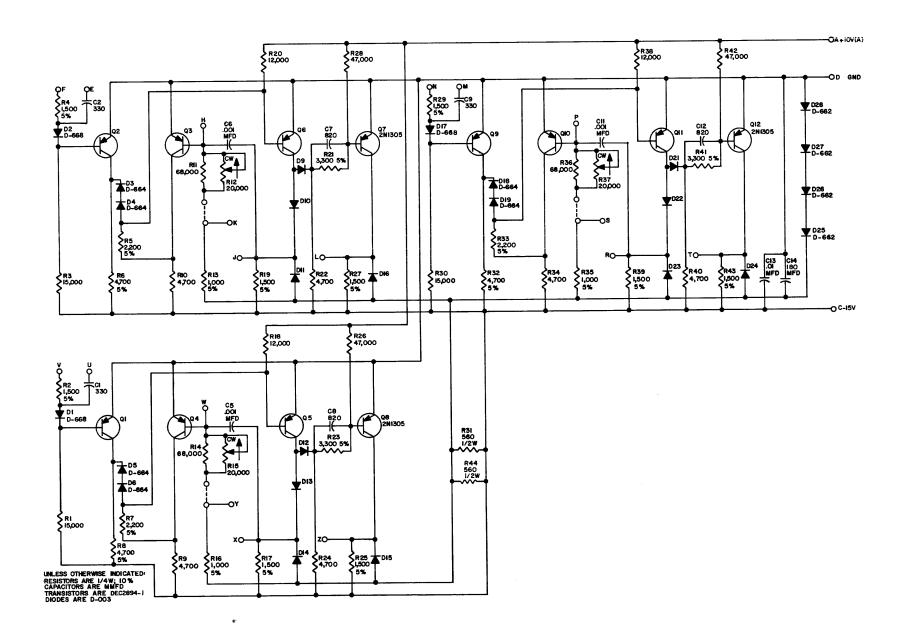

| RS-C-4523 | Manchester Reader and Writer              | 6-40        |

| RS-B-4604 | Pulse Amplifier                           | 6-41        |

| RS-B-4605 | Pulse Amplifier                           | 6-41        |

| RS-B-4606 | Pulse Amplifier                           | 6-42        |

| RS-B-4671 | BCD Light Driver                          | 6-42        |

| RS-B-4689 | Indicator Driver                          | 6-43        |

| RS-B-6102 | Inverter                                  | 6-43        |

## CHAPTER 1

#### 1-1 GENERAL DESCRIPTION

The Type 552 DECtape Control transfers binary data between one of two types of DEC digital computers (i.e., PDP-5 or PDP-8) and up to eight transport drives (e.g., four Type 555 transports, eight TU55 transports or any 8-drive combination). A Type 555 DECtape transport contains two independent tape drives with relay logic to select and control the tape motion of each drive; a Type TU55 contains a single drive with solid-state logic.

Binary information is transferred between the tape transport and the computer as one 12-bit computer word approximately every 133-1/3 µsec. In writing, the Type 552 DECtape Control disassembles 12-bit computer words so that they are written in four successive lines on tape. Transfers between the computer and the control always occur in parallel for a 12-bit word. Data transfers use the data-break (high-speed channel) facility of the computer. As the start and end of each block are detected by the mark-track detection circuits, the control raises a DECtape (DT) flag which causes a computer program interrupt. The program interrupt is used by the computer program to determine the block number. When it determines that the forthcoming block is the one selected for a data transfer, it selects the read or write control mode. Each time a word is assembled or DECtape is ready to receive a word from the computer, the control raises a data flag. This flag is connected to the computer data-break facility to signify a break request. Therefore, when each 12-bit computer word is assembled, the data flag causes a data break and initiates a transfer. By using the mark-channel decoding circuits and data-break facility in this manner, computation in the main computer program can continue during tape operations. The functions performed by the Type 552 DECtape Control in these operations are described in detail in Chapters 2, 3, and 4.

#### 1-2 TYPE 552 CHARACTERISTICS

Table 1-1 contains a summary of the characteristics of the Type 552 DECtape Control plus its associated transport equipment.

TABLE 1-1 SUMMARY OF EQUIPMENT CHARACTERISTICS FOR THE TYPE 552 DECTAPE CONTROL

| 552 Control | 21 inches high, 19 inches wide for equipment which operates four Type 555 or eight Type TU55 transports or any combination thereof, up to eight drives. |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | , ,                                                                                                                                                     |

## TABLE 1-1 SUMMARY OF EQUIPMENT CHARACTERISTICS FOR THE TYPE 552 DECTAPE CONTROL (continued)

555 Transport 10-1/2 inches high, 19 inches wide

TU55 Transport 10-1/2 inches high, 19-1/2 inches wide

Cabinet 69-1/8 inches high, 22-1/4 inches wide, 27-1/16 inches

deep. Will hold a maximum of one Type 552 Control and

three Type 555 Dual Transports.

Weight

552 Control 30 pounds

555 Transport 65 pounds (rack mounted)

TU55 Transport 65 pounds (rack mounted)

Cabinet 555 pounds

Power Requirements

552 Control 115v, 60 cps, 4 amp.

A Type 728 and a Type 734 Power Supply are included in

the Type 552 Control.

555 Transport 115v, 60 cps, 3.2 amp maximum, 1.5 amp idle.

TU55 Transport  $115v \pm 10\%$ , 60 cps, 2.0 amp maximum, 1.5 amp idle.

Cabinet 115v, 60-cps source capable of delivering 20 amp.

#### Tape Characteristics

a. 260 feet of 0.75 inch, 1.0 Mylar tape per 3.5-inch reel.

b.  $350 \pm 55$  lines per inch.

c. 849,036 usable lines per tape.

d. 60 lines per control zone.

e. 4096 is the maximum number of addressable blocks per reel.

f. Number of words in a block must be divisible by 3.

g.  $N_B = \frac{212112}{N_{M} + 15} - 2$   $N_B = decimal number of blocks$

$N_W^{-1}$  number of words per block

h. Capacity for 190, 000 12-bit words in blocks of 129 words.

#### Word Transfer Rate

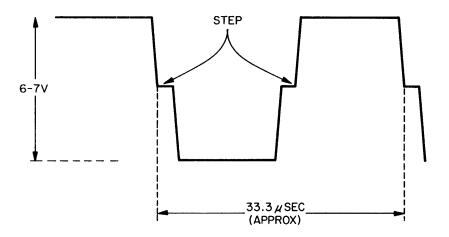

- a. One tape line is read or written every 33-1/3 µsec.

- b. A 12-bit word is read and assembled or disassembled and written in 133-1/3 usec.

- c. In reverse direction, the transfer rate varies by 20% as the effective reel diameter changes.

## TABLE 1-1 SUMMARY OF EQUIPMENT CHARACTERISTICS FOR THE TYPE 552 DECTAPE CONTROL (continued)

#### Word Transfer Rate (continued)

- d. Transfers require 4.5% of PDP-5 cycles after the initial 200-msec start time.

- e. Transfers require 1.2% of PDP-8 cycles after the initial 200-msec start time.

#### Addressing

- a. Mark and timing channels allow searching for a particular block.

- b. Start time is <200 msec, stop time is <150 msec, turn-around time is <200 msec.

- c. Start and stop distances are approximately 8 inches.

- d. When a command to reverse direction is issued at a given tape location, the system is up to speed when that same location passes the head after turnaround.

#### Input Signals to Transport from Control

| Commands*    | FORWARD normally complementary levels                                                                 |

|--------------|-------------------------------------------------------------------------------------------------------|

|              | STOP                                                                                                  |

|              | ALL HALT stops transport when computer halts.                                                         |

| Unit Select* | Select 1 through select 8                                                                             |

| Control      | POWER CLEAR is a standard DEC negative pulse to prevent tape motion when computer power is turned on. |

#### Output Signal from Transport to Control

| Humidity              | 10-90% relative humidity              |

|-----------------------|---------------------------------------|

| Operating Temperature | 50–95°F ambient                       |

| Thermal Dissipation   | 2150 Btu/hour                         |

| Control               | WRITE ENABLE (ground level assertion) |

NOTE: The magnetic tape manufacturer recommends 40-60% relative humidity and 60°-80°F as an acceptable operating environment for DECtape.

<sup>\*</sup>These signals are approximately -3v or floating when supplied by a control unit designed to operate the Type 555 Dual DECtape transport which uses relay switching logic circuits; or are standard DEC logic levels of ground and -3v when supplied by a control unit designed specifically to drive the TU55.

#### 1-2.1 Physical Details

The Type 552 DECtape Control is mounted in the lower three panels of a standard DEC computer cabinet. This arrangement requires three module mounting panels plus three standard 50-terminal interface connectors. When so mounted, up to three Type 555 or Type TU55 DECtape transports may be installed in the same cabinet.

The standard DEC computer cabinet is constructed with a welded steel frame and sheet steel covering. Double doors on the front and rear are held closed by magnetic latches. Power supplies and controls are mounted inside the rear double doors on a full-width plenum door latched by a spring-loaded pin at the top. Module mounting panels are mounted behind the double door in front with the wiring side facing outward. Fans at the bottom of the bay draw cooling air through dust filters, pass it over the electronic components, and exhaust it through the wiring and other openings in the front and top of the cabinet. Four casters provide mobile support for the system. The rear plenum door contains blank panels in the space not used by components. Control equipment used with the PDP-5 requires a Type 728 Power Supply mounted near the bottom of the door. AC power for this supply is furnished through a utility outlet which is controlled by the PDP-5 power control. A Type 734 Power Supply mounted at the top rear of the PDP-5 provides marginal-check power for the control equipment. Control equipment used with the PDP-8 requires two Type 728 Power Supplies and one Type 834 Power Control. These units are mounted near the bottom of the plenum door and a Type 734B Power Supply for marginal-check power is mounted at the top.

Standard DEC computer cabinets have access doors which extend 8-3/4 inches to the front of the cabinet and a plenum door which extends 13-3/4 inches to the rear. At least 3 feet should be allowed at both front and rear for access and maintenance. Cabinets may be bolted together at the sides to form contiguous units.

#### 1-2.2 Electrical Details

A cable rated at 6.5 amp (8 amp surge) at 115v, 60 cps furnishes power for the Type 552 DECtape Control. This cable is terminated by a Hubbell Twist Lock plug rated at 30 amp, 25 vac.

Signal connections to and from the tape drives are made through 22-pin Amphenol connectors (similar to those used for the logic modules). When viewed from the rear, the connectors at the left of the top logic panel are for the head bus, the pair at the right of the center panel are for the control and selection buses. Signal connections from PDP-5 are made through two cables terminated by 50-pin Amphenol plugs. Three 50-pin receptacles are mounted wiring-side out at the right front of the panel just above the logic panel. A standard PDP-5 programmed in/out transfer cable plugs into the left receptacle, a data-break transfer cable plugs into the right. The center receptacle is bused to the left, allowing the programmed transfer bus to extend to other peripheral devices. PDP-8 signals are connected through eight twisted-pair cables which terminate in DEC FLIP CHIP Type W021 Cable Terminations. These terminations

plug directly into the upper sockets at the left of the connector panel above the logic. The lower FLIP CHIP sockets are bused to the upper, so that both the programmed-transfer bus and the data-break bus may extend to other peripheral devices. Either a PDP-5 or PDP-8 may be connected to the Type 552 DECtape Control, but not simultaneously. No logic or wiring changes are required to adapt the control equipment to either computer.

Signals between the Type 552 DECtape Control and the computer are the standard voltage levels for the DEC 4000-series modules, as stated in the DEC System Modules Catalog. Control and selection signals between the Type 552 and the tape transport are designed to operate relays. The energizing signal is -15v at 30 ma maximum; the common return is at ground level. During writing, the head bus carries 200 ma in either direction with a 20v peak-to-peak waveform symmetrical with respect to ground. When reading, the peak-to-peak head-voltage waveform is between 4 and 6 mv when the tape is up to speed. The internal logic for the Type 552 consists of DEC 4000-series logic modules, except for two 1000-series diode modules (which act as pulse gates for the standard 400 nsec pulses), and two 6000-series inverter modules required for fast rise-time applications. All internal signals are standard 4000-series levels and pulses, except those for the read/write amplifiers and relay drivers. Power for the Type 552 is the conventional -15v collector supply, +10v base bias supply.

The types and number of FLIP CHIP modules used in the Type 552 DECtape Control are listed in DEC engineering drawing ML-A-552-0-15 of Chapter 6. Module locations in the three mounting panels are shown in DEC drawing UML-D-552-0-18. An explanation of the conventions in this drawing is given in Chapter 5.

#### 1-3 SCOPE OF MANUAL

This manual is intended to aid personnel in the maintenance of the Type 552 DECtape Control. The equipment is discussed primarily from a maintenance point of view, but some information is given on operation and associated controls and indicators. Pertinent documents listed in the following subsection give more complete information on operation from a programmer's viewpoint. Since the DECtape control is one element of a computer/control/transport system, the reader is advised to become familiar with the internal operations of both the computer and the appropriate transports. Of special importance are sections concerning program interrupts, programmed in/out transfers and the data-break facility in the computer; and the select and motion-control logic in the tape transport. Detailed descriptions of the instruction repertoire and programming practice for a particular computer can be found in the PDP-5 and PDP-8 hand-books. Information on the logic and motion control of the Type 555 and Type TU55 DECtape transports can be obtained from the maintenance manuals for the particular transport.

#### 1-4 PERTINENT DOCUMENTS

The following DEC documents contain material which supplements information in this manual. These documents may be obtained from the nearest DEC office or from:

Digital Equipment Corporation 146 Main Street Maynard, Massachusetts

#### 1-4.1 Manuals

<u>Digital FLIP CHIP Modules (C105)</u> - Specifications and descriptions of each FLIP CHIP module, plus simplified explanation of selection and use of these modules in numerous applications.

System Modules (C100) - Specifications and descriptions of basic system modules, plus simplified explanation of selection and use of these modules in numerous system applications.

<u>PDP-5 Handbook (F-55)</u> - Detailed information on the function, instructions, and programming of the three major system elements of the computer.

<u>PDP-5 Software Package</u> - Perforated program tapes and descriptive matter for the program assembly language (PAL) utility subroutine and maintenance programs.

<u>PDP-8 Handbook (F-85)</u> - Programming and operating information for the computer, including brief instructions on the Type 552 DECtape Control.

<u>PDP-8 Maintenance Manual (F-87)</u> - Complete information on the internal operations of PDP-8 logic, memory, basic in/out, and processor options.

<u>PDP-8 Programming Manual (Digital-8-27-U)</u> - Programs for PDP-8. These programs can also be used without change on PDP-5. Complete descriptions of DECtape subroutines designed for assembly with an object program, the DECtape library system, and the DECtape utility routines.

<u>Type 555 DECtape Transport Maintenance Manual</u> – Transport drive logic and internal operations, plus preventive and corrective maintenance instructions.

<u>Type TU55 DECtape Transport Maintenance Manual</u> – Transport drive logic and internal operations, plus preventive and corrective maintenance instructions.

#### 1-4.2 Engineering Drawings

| Drawing Number | <u>Title</u>                            |

|----------------|-----------------------------------------|

| FPL-C-552-0-1  | 552 DECtape                             |

| PL-A-552-0-1   | 552 DECtape Parts List                  |

| BS-D-552-0-3   | Status Timing and Mark-Track Decoding   |

| BS-D-552-0-4   | Flag, Error Detection, and Write Enable |

| Drawing Number        | <u>Title</u>                                              |

|-----------------------|-----------------------------------------------------------|

| BS <b>-</b> D-552-0-5 | Longitude Parity Buffer and Memory Address Control        |

| BS-D-552-0-6          | Read/Write Buffer, Data Buffer, and Read/Write Amplifiers |

| BS -D-552-0-7         | RWB, DB, WB Controls                                      |

| BS-D-552-0-8          | Motion and Function Control                               |

| WL-B-552-0-16         | Wiring List Type 552 DECtape Control                      |

| UML-D-552-0-14        | Utilization Module Location                               |

| UML-D-552-0-18        | Utilization Module Location                               |

| ML-A-552-0-15         | Module List                                               |

#### 1-4.3 Replacement Schematics

| Drawing Number    | Title                             |

|-------------------|-----------------------------------|

| RS <b>-72</b> 8-5 | Power Supply 728                  |

| RS-B-734B-2       | Variable Power Supply 734B        |

| RS-B-1033-1       | Microtape Attenuator 1033         |

| RS-B-1113-6       | Diode 1113                        |

| RS-1501-5         | Level Standardizer 1501           |

| RS-1982-5         | Inhibit Driver 1982               |

| RS-B-4102-4       | Inverter 4102                     |

| RS-B-4113-9       | Diode 4113                        |

| RS-B-4114-7       | Diode 4114                        |

| RS-B-4115-7       | Diode 4115                        |

| RS-B-4117-7       | Diode 4117                        |

| RS-B-4127-6       | Capacitor Diode Inverter 4127     |

| RS-B-4129         | Capacitor Diode Inverter 4129     |

| RS-4151-8         | Binary-to-Octal Decoder 4151      |

| RS-4215-8         | 4-Bit Counter 4215                |

| RS-4217-4         | 4-Bit Counter 4217                |

| RS-D-4260-1       | Mark-Track Decoder 4260           |

| RS-B-4303-17      | Integrating One-Shot 4303         |

| RS-B-4401-12      | Clock 4401                        |

| RS-C-4523-7       | Manchester Reader and Writer 4523 |

| RS-4671-4         | BCD Light Driver 4671             |

In addition to the above documents, complete sets of library programs are available for each computer using DECtape systems.

A complete set of reduced engineering drawings and replacement schematics for the Type 552 DECtape Control is in Chapter 6. The engineering drawings are in addition to the complete set of full-size drawings forwarded with each DECtape control. As explained in Chapter 6, all maintenance personnel should use only the full-size engineering drawings for work on the equipment, because the full-size drawings include variations peculiar to an individual installation.

## CHAPTER 2 PRINCIPLES OF OPERATION

This chapter describes the principles of operation of the Type 552 DECtape Control System by giving functional descriptions of each system element and then summarizing the programmed operation of the control system containing these elements. Brief descriptions of DECtape format, instructions, and control modes provide a background for understanding the functional operation of the system. The pertinent documents listed in Chapter 1 contain more detailed information on these programming features.

#### 2-1 DECTAPE FORMAT

Format of the DECtape used in the DECtape transport is an important factor in the operation of the Type 552 DECtape Control. DECtape provides for ten tracks, of which three pairs are available for data and two pairs for timing and mark information (see Figure 2-1). A 10-track recording head reads and writes the five duplexed channels of the DECtape. Duplication of each track by nonadjacent read/write heads, wired in series, eliminates most dropouts due to noise and dust, and minimizes skew problems. The location of the redundant head eliminates most cross talk between tracks. In addition, the location of the timing tracks along the edges of the tape permits strobing on the analog sum of the timing-track signals and guarantees reading of the data tracks when they are in the most favorable position. The location of the data tracks in the middle of the tape also minimizes the effects of skew.

Figure 2–1 DECtape Track Allocation Showing Redundantly Paired Tracks

Information is stored on the tape in block form (see Figure 2-2). Block length is flexible and determined by information on the mark channel. A complete reel of tape (849,036 lines) can be divided into any number of blocks up to 4096. Usually, a uniform block length is established over the entire length of a reel of tape by a program which writes mark and timing information at specific locations. However, the ability to write variable-length blocks is useful for certain data formats; for example, where small blocks containing index or tag information need to be alternated with the large blocks of data.

Figure 2-2 Basic Six Line DECtape Unit

Each block contains two types of words which are assembled by the Type 552 DECtape Control --data and control words (see Figure 2-3). Because DECtape has no inter-record gaps, control words separate the data portions of adjacent blocks. Although control words usually occupy six lines, only the last four lines are used for the PDP-5 and PDP-8. Control words record address and checking information. They provide compatibility between DECtape written on any DEC 12-, 18-, or 36-bit computer. Data words contain stored information and occupy four lines on tape (12 bits). To maintain compatibility with the mark-channel format, data words are recorded in 12-line segments (12 being the lowest common multiple of 6-line marks and 4-line data words) which correspond to three 12-bit data words.

Figure 2-3 DECtape Control and Data Word Assignments

Block numbers normally occur in sequence from 1 to N. There is one block numbered 0 and one block N + 1. Programs are entered with a statement of the first block number to be used and the total number of blocks to be read or written. The maximum number of blocks is determined by the following equation in which  $N_B$  = decimal number of blocks, and  $N_W$  = decimal number of words per block. ( $N_W$  must be divisible by 3.)

$$N_B = \frac{212112}{N_W + 15} - 2$$

#### 2-1.1 Mark-Channel Format

The mark channel is the key to the overall computer system. Six-bit serially stored codes (called marks) on the mark track initiate controls which raise flags in the program, create sequence breaks, detect block mark numbering and block ends, and protect control portions of the tape (see Figure 2-4). The DECtape control unit automatically identifies these codes. The mark track also provides for automatic bidirectional compatibility, variable block formatting, and end-of-tape sensing.

Figure 2-4 DECtape Mark Track Format (Assumes 256<sub>10</sub> Data Words Per Block)

Because the DECtape system allows searching as well as reading and writing in both directions of tape motion, the mark track is often read in reverse. In the reverse case, not only are the mark-track bits read serially in reverse order, but also (since the polarity of pulses is reversed when the tape moves

backward) the complement is read. The complement of a number with the bits reversed is defined as the complement obverse. The mark-track format has been carefully selected to be symmetrical so that the logic for reading in the reverse direction is exactly the same as that for forward reading. The complement obverse of the end-of-tape mark becomes the beginning-of-tape mark, and the end-of-data mark becomes the beginning-of-data mark.

The standard mark track uses the serial code of 6-bit characters to divide the tape into words. Codes are written on the mark track opposite word locations to identify the type of information stored at that location on tape. Block addresses are written for both forward and reverse directions and identified by two types of mark codes. A checksum is written at each end of the block. The first checksum written is -0 ( $-777777_8$ ). This information is stored in a register in the computer. As each succeeding data word is read from the block, a total is kept that represents the sum of the words in the block. (Data words are added to -0.) Since the second checksum is the complement of the total, the addition of this number to the register should cause the appearance of -0. The control uses the final marks to establish synchronism and raise block-end flags. Data marks locate data words.

#### 2-2 DECTAPE INSTRUCTIONS

The ten basic instructions used for the operation of the Type 552 DECtape Control system are summarized in Table 2–1. A more detailed description of these instructions, equally applicable to the PDP-5 and PDP-8, is in the PDP-8 Programming Manual (Digital-8-27-U).

Included in the basic instructions are those for eight modes of operation which are loaded into the function register (see Figure 2-5) during the MMLF command. These control modes are described briefly in the following subsection. Also included are the status-bit assignments which are loaded into status register during the MMRS command. Table 2-2 lists the meanings of these bit assignments.

Operation Octal Mnemonic Load select register from contents of AC bits 2-5 and clear **MMLS** 6751 DECtape (DT) flag. DT flag is automatically set approximately 70 msec after this IOT. Load motion register from contents of AC bits 7-8 and clear 6752 **MMLM** DT flag. DT flag is automatically set approximately 70 msec after this IOT. Load function register from contents of AC bits 9-11, then **MMLF** 6754 clear the AC. The octal code of these three bits 9-11 establishes the following DECtape control modes:

TABLE 2-1 DECTAPE INSTRUCTION LIST

TABLE 2-1 DECTAPE INSTRUCTION LIST (continued)

| Mnemonic | Octal | Operation                                                                                                                                                                            |  |  |

|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|          |       | <pre>0 = Move 1 = Search 2 = Read data 3 = Read all bits 4 = Write data 5 = Write all bits 6 = Write mark and timing 7 = Move and examine mark channel.</pre>                        |  |  |

| MMSF     | 6761  | Skip if DT flag is a 1.                                                                                                                                                              |  |  |

| MMCC     | 6762  | Clear memory address counter (MAC).                                                                                                                                                  |  |  |

| MMLC     | 6764  | Load MAC from content of AC bits 0-11 and then clear the AC. (1's transfer).                                                                                                         |  |  |

| MMML     | 6766  | Clear and load MAC from content of AC bits 0–11 and then clear the AC ${\color{blue} \bullet}$                                                                                       |  |  |

| MMSC     | 6771  | Skip if error flag is a 1.                                                                                                                                                           |  |  |

| MMCF     | 6772  | Clear error flag and DT flag.                                                                                                                                                        |  |  |

| MMRS     | 6774  | Read status bits into the content of AC bits 0-7.                                                                                                                                    |  |  |

|          |       | The bit assignments are:                                                                                                                                                             |  |  |

|          |       | AC0 = DT flag AC1 = Error flag AC2 = End (selected tape at end point) AC3 = Timing error AC4 = Reverse tape direction AC5 = Go AC6 = Parity or mark channel error AC7 = Select error |  |  |

#### 2-3 CONTROL MODES

The eight modes of operation which are loaded into the function register during the MMLF command (see Table 2-1) are described briefly in the following subparagraphs.

- a. <u>Move</u> Initiates motion of the selected transport tape in either direction.

Mark-channel errors are inhibited in this mode.

- b. <u>Search</u> As the tape is moved in either direction, the sensing of a block mark causes both the data flag and the DECtape (DT) flag to rise. The data flag requests a computer data break for depositing the block number in the core memory at the

address held in the memory address register (MAC). The DT flag initiates a program interrupt which causes the program to jump to a particular subroutine; e.g., a subroutine which is responsible for checking the block numbers by using either the block number stored during this operation or by counting the number of times the DT flag rises.

- c. Read Data This mode reads a block of data in either direction, raises the data flag to cause a data break each time a 12-bit word is to be transferred, and raises the DT flag to initiate a program interrupt at the end of the data block. The program is responsible for controlling tape motion at the end of a block transfer and must stop motion or change the contents of the function register when the DT flag rises. The transport continues reading until taken out of the read-data mode.

- d. Read All Bits In this mode, the three information channels are continuously read and transferred to the computer. This mode is similar to the read-data mode except that the DT flag rises each time the data flag rises. The read-all-bits mode is used to read an unusual tape format which is not compatible with the read-data mode. The DT flag does not cause an interrupt when in this mode.

- e. <u>Write Data</u> This mode writes a block of data on tape in either direction, raises the data flag to effect each transfer, and raises the DT flag at the end of the block as in the read-data mode.

- f. <u>Write All Bits</u> This special mode of operation is used to write information at all positions without regard to blocks (such as in writing block numbers). Except that it applies to writing, this mode is similar to the read-all-bits mode. The DT flag does not cause an interrupt in this mode.

- g. Write Mark and Timing This mode is used to write on the timing and mark channels for establishing or changing block length.

- h. <u>Move and Examine Mark Channel</u> This mode is similar to the move mode mentioned above except that the control examines the mark channel and causes a program interrupt whenever an expected mark is absent.

#### 2-4 FUNCTIONAL DESCRIPTION

The basic functional elements of the Type 552 DECtape Control (plus its PDP-5/8 computer and 555/TU55 transport interfaces) are shown in Figure 2-5. In this figure, numerals in the lower right corner of the blocks indicate bit-capability of the device, while numerical subscripts on the signal flow lines indicate the bit assignments in the signal; e.g.,  $AC_{9-11}$  indicates that accumulator bits 9-11 are assigned for use in the signal. Brief descriptions of the functional elements in Figure 2-5 are given in the following subsections.

Figure 2–5 Block Diagram of Type 552 DECtape Control Plus PDP-5/8 and Transport Interface Elements

#### 2-4.1 Data Buffer (DB)

This 12-bit register serves as a storage buffer for data to be transferred between DECtape and the computer memory buffer register. During a read operation, information sensed from the tape is

transferred into the DB from the read/write buffer for subsequent transfer to the computer during a databreak cycle. During a write operation, the DB receives information from the computer and transfers it to the read/write buffer for disassembly and recording on tape. The DB, therefore, synchronizes data transfers by allowing transfers between the computer and the read/write buffer as a function of the tape timing.

#### 2-4.2 Read/Write Buffer (R/WB)

This 12-bit register is composed of three 4-bit shift registers. During reading, one bit from each information channel is read into a separate segment of the R/WB and shifted right or left as a function of the direction of tape movement. When four tape positions have been read, the contents of the R/WB are set into the DB as an assembled 12-bit computer word. During writing, the contents of each segment of the R/WB are shifted serially to the write register (one bit from each of the three segments of the R/WB is transferred into the write register at a time to provide the data to be written at one line) for recording on tape.

#### 2-4.3 Write Register

This 3-bit register is alternately loaded from the R/WB and complemented to write the phase-coded information on tape.

#### 2-4.4 Read Register

During reading, this 3-bit register is loaded with one bit from each of the three information channels of the read head and transferred to the R/WB.

#### 2-4.5 Device Selector (DS)

The device selector is a gating circuit which produces in/out transfer (IOT) pulses necessary to initiate operation of the DECtape system and to strobe information into the computer. This selector accepts all three in/out pulses (IOP) from the computer and decodes the contents of bits 3-8 of the IOT instruction in the computer memory buffer to determine whether the IOPs are addressed to DECtape control. When the control is addressed, the selector generates an IOT pulse for each IOP sent from the computer.

#### 2-4.6 Select Register

This 4-bit register is loaded under the program control to specify the particular DECtape drives (eight tape drives available) selected for operation by the DECtape control. A 4-bit code in accumulator octal bits 2-5 is used for the selection and is decoded by the decoder at the right of the select register.

#### 2-4.7 Decoder

Thirty-five msec after receipt of a select command from the select register, this decoder develops a signal for the unit relays of the selected DECtape transport. When enabled by a go command from the motion register, the decoder (to the right of the function register) asserts one of the seven function signals in the FR for use by control.

#### 2-4.8 Motion Register

This 2-bit register contains a GO/STOP flip-flop and a FORWARD/REVERSE flip-flop which control the motion of the selected tape drive. The register is set under program control.

#### 2-4.9 Status Register

This register contains eight gates which produce load pulses for bits 0-7 of the accumulator upon receipt of a read-status instruction addressed to control. The instruction generates an in/out transfer (IOT) pulse which drives all eight gates. Appropriate setting of the accumulator bits is effected according to the DECtape and error flags, the four error conditions, and two additional levels (GO and REVERSE), which assert tape-motion commands to the selected drive. The GO flip-flop is loaded from the motion register to initiate tape motion 35 msec after an instruction loads the motion register. Simultaneously the REVERSE flip-flop is loaded. Table 2-2 contains a summary of the meanings of accumulator bits 0-7.

TABLE 2-2 SIGNIFICANCE OF ACCUMULATOR BITS 0-7

| AC Bit | Condition    | Significance                                                                                                                                                           |

|--------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC0    | DECtape flag | Control has completed a processing operation, or has recognized a new motion or select command and is requesting an interrupt.                                         |

| AC1    | Error flag   | One of the four error conditions has occurred; thus a 1 is in accumulator bits 2, 3, 6, or 7 and control is requesting a program interrupt.                            |

| AC2    | End          | Tape at the selected drive is in the end zone.                                                                                                                         |

| AC3    | Timing Error | Computer has failed to honor a program interrupt or data-<br>break request, or new motion or select commands were issued<br>before the last command could be executed. |

TABLE 2-2 SIGNIFICANCE OF ACCUMULATOR (continued)

BITS 0-7

| AC Bit | Condition                      | Significance                                                                                                                                  |

|--------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| AC4    | Reverse                        | Last tape motion command specifying GO also specified REVERSE.                                                                                |

| AC5    | Go                             | Control currently commands selected-tape drive to move tape.                                                                                  |

| AC6    | Parity or Mark.<br>Track Error | An error occurred in the timing or mark channels, or when reading in the data mode, a parity error was detected at the end of the last block. |

| AC7    | Select Error                   | Control is unable to address one and only one tape drive, or has been commanded to write at a drive set to WRITE LOCK.                        |

#### 2-4.10 Function Register

This 3-bit register specifies the function to be performed by the control in any tape operation. Upon receipt of DECtape instructions, the function register is loaded from bits 9-11 of the accumulator. The octal code of these three bits establishes the eight DECtape control modes listed in Table 2-1. Any instruction that loads the function register also clears the accumulator.

#### 2-4.11 Memory Address Counter (MAC)

This 12-bit register specifies an address in computer core memory to be used for each word transfer. During program initialization, the starting address of a transfer is set into MAC from the accumulator. During the transfer, the address in MAC is transferred into the computer memory address register for each data word. The contents of MAC are incremented by 1 at the conclusion of each word transfer, so that transfers occur between successive addresses of computer core memory and tape, regardless of tape direction.

#### 2-4.12 Window (W)

This 9-bit register serves as a control signal generator for the DECtape system. The mark-channel data is stored in the W, and control signals are generated as a function of the mode of operation

in progress and the contents of the W. For example, in the search mode, when the W detects a block mark, control signals are generated to raise the DECtape (DT) flag to indicate the presence of a block number in the DB and signal the start of data block to the computer.

#### 2-4.13 Longitudinal Parity Buffer (LPB)

This 6-bit register performs a parity check of the information in the three information channels. Essentially, the check reads the number of binary 0's in each half of a 12-bit data word and forms a parity bit to be recorded in the checksum control word at the end of the data block. This operation is performed by setting the information read from two consecutive tape positions into the LPB, and then complementing a bit of the LPB if the corresponding bit of the R/WB contains a 0. After reading a block of data, the LPB holds a number which indicates the parity of bits 0 and 6, 1 and 7, etc. A 1 in the LPB at this time indicates odd parity, and a 0 indicates even parity. This information is compared with the data stored in the checksum control word during reading and generates the checksum during writing. If the data read is not equal to the checksum, the parity or mark-channel-error flip-flop is set to 1.

#### 2-4.14 Error Flag

Four error conditions raise this flag. When the flag rises, it initiates a program interrupt to allow the computer interrupt subroutine to determine the condition of Type 552 DECtape Control by means of a read status command. The four error conditions indicated are:

| Condition    | Meaning                                                            |  |  |  |  |

|--------------|--------------------------------------------------------------------|--|--|--|--|

| End          | The tape of the selected transport is in the end zone and tape     |  |  |  |  |

|              | motion is stopped automatically. Under these conditions, end       |  |  |  |  |

|              | is an error if it is not expected by the program in process, or it |  |  |  |  |

|              | is a legitimate signal used to indicate the end of a normal oper-  |  |  |  |  |

|              | ation (such as rewind) if it is anticipated by the program. If the |  |  |  |  |

|              | transport is not selected when the tape enters the end zone, this  |  |  |  |  |

|              | end signal is not given, tape motion is not stopped automatically, |  |  |  |  |

|              | and the tape can run off the end of the reel.                      |  |  |  |  |

| Timing Error | The program is not able to keep pace with the tape transfer rate,  |  |  |  |  |

|              | or a new motion or select command was issued before the previous   |  |  |  |  |

|              | command was completely executed.                                   |  |  |  |  |

| Condition                     | Meaning                                                                                                                                                                                                                        |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parity or Mark–Track<br>Error | Indicates that during the course of the previous block transfer a data parity error was detected, or one or more bits have been picked up or dropped out from either the timing track or the mark track.                       |

| Select Error                  | Signifies that a tape-transport unit select error has occurred (for example, more than one transport in the system has been assigned the same select code), or that no transport has been assigned the programmed select code. |

In summary, a select error indicates an error by the operator; a timing error is a program error; and a parity or mark-track error indicates an equipment malfunction. Under certain conditions, the end may also be an indication of equipment malfunction.

#### 2-4.15 DECtape Flag (DT)

This flip-flop serves as an indicator of DECtape system operation to the computer and is connected to the computer program interrupt facility. The control mode in operation at the time determines the function of the DT flag as follows:

- a. In the search mode, the DT flag rises each time a block mark (block number) is read to indicate the beginning of a new block and to allow programmed determination of the block number which just passed the read/write head.

- b. In read-data or write mode, the DT flag rises at the end of each block to indicate the end of a data block. Under these conditions, the computer program can sense for this flag to determine when the transfer is complete.

- c. In read-all-bits or write-all-bits mode, the DT flag rises to indicate completion of each 12-bit word transfer. Since block marks are not observed in these modes, the computer program can use this flag to count the number of words transferred as a means of determining tape location.

#### 2-4.16 Data Flag

This flag is raised each time the DECtape system is ready to transfer a 12-bit word with the computer. When raised, the flag produces a computer data break.

#### 2-5 PROGRAMMED OPERATION

The prerecording of a reel of DECtape (prior to its use for data storage) is accomplished in two passes. During the first pass, the timing and mark channels are placed on the tape. During the second pass, the forward and reverse block-mark numbers, the standard data pattern, and the automatic parity checks are written. The DECTOG program (see PDP-8 Programming Manual) performs these functions. Prerecording utilizes the write-timing-and-mark-channel control mode plus a manual switch in the DEC-tape control to write on the timing and mark channels, to activate a clock which produces the timing-channel recording pattern, and to enable flags for program control. Unless this control mode and switch are used simultaneously, the writing on the mark or timing channels is physically impossible. A red indicator lights on all transports associated with the control when the manual switch is in the ON position. Only under these conditions does the write register and the write amplifier (which writes on information channel 1, bits 0, 3, 6, and 9) write on the mark channel.

Two PDP-8 in/out transfer (IOT) DECtape instructions initiate operation of the DECtape. The first instruction (MMMM) loads the select register, motion register, and function register by means of instruction 6757 (combining MMLS, MMLM, and MMLF). A second instruction MMML 6766 (combining MMCC and MMLC), loads the memory address counter (MAC) with the core memory address for use in storing the block number during searching. After initiating DECtape operation, the program always checks immediately for errors using the MMSC instruction. This instruction is also used at the end of each transfer. A program always starts the DECtape system in the search mode to locate the block number selected for transfer. When the block number has been located, the transfer is accomplished by loading the function register with the read-data or write-data mode.

In searching, the transport reads each block number and transfers it to the control. The control raises the DT flag upon receipt of each block number and stores the number in the computer core memory at the address in MAC. The computer program then samples the DT flag and either counts the number of blocks passed or reads the block number from core memory and compares it with the number it is seeking. The results of data obtained in this way are used to further control the search operation. Upon determining that the forthcoming block is the one selected for a data transfer, the program loads the function register with either the read-data or write-data mode. Entering another mode discontinues the search mode. The computer then sets into the MAC the starting address to be used for the first core memory address of the transfer.

When the start of the data position of the block is detected, the data flag is raised to initiate a data break each time the DECtape system is ready to transfer a 12-bit word. Therefore, the main computer program continues running but is interrupted approximately every 133-1/3 µsec during a data break for the transfer of a word. Transfers occur between DECtape and successive core memory locations, commencing at the address previously set into MAC. The size of the selected tape block determines the

number of words transferred. At the conclusion of the block transfer, the DT flag is raised, and a program interrupt occurs. The interrupt subroutine checks the DECtape error flag to determine the validity of the transfer and either initiates a search for the next information to be transferred or returns to the main program.

During all normal writing transfers, a checksum (the 6-bit exclusive OR of the words in the data block) is computed automatically by the control and is automatically recorded as one of the control words immediately following the data portion of the block. This same checksum is used during reading to determine that the data playback and recognition take place without error.

The program can select any one of the eight tape drives. After using a particular drive, the program can stop the drive currently being used and select a new drive, or can select another drive while permitting the original selection to continue running. Because several transports may be used simultaneously, this is a particularly useful feature when rapid searching is desired. Caution must be exercised, however, because, although the earlier drive continues to run, no tape-end detection or other sensing takes place. Automatic end sensing that stops tape motion occurs in all modes, but only in the selected tape drive.

Whenever either the motion or select code is changed, the program must wait until the DT flag is set to 1 before giving another motion or selection command. In other words, to prevent a timing error, all operations of the currently selected drive must be completed before issuing a new select code.

#### 2-6 AVAILABLE SOFTWARE

PDP-5/8 software (see PDP-8 Programming Manual Digital-8-27-U) includes the following:

- a. Subroutines which the programmer may easily incorporate into a program for data storage, logging, data acquisition, data buffering (queueing), etc.

- b. A library calling system for storing named programs on DECtape and calling them with a minimal size loader.

- c. Programs for preformatting tapes controlled by the content of the switch register to write the timing and mark channels, to write block formats, to exercise the tape and check for errors, and to provide ease of maintenance.

The series of subroutines will read or write any number of DECtape blocks; read any number of 129-word blocks as 128 words (or one memory page) in which 200 octal locations equal 126 decimal locations; or search for any block (used by read and write, or to position the tape). These programs are assembled with the user's program and are called by a jump-to-subroutine (JMS) instruction. The program interrupt detects the setting of the DECtape (DT) flag, allowing the main program to proceed while the

DECtape operation is being completed. A program flag is set when the operation has been completed. The program may thus effectively allow concurrent operation of several input/output devices with the DECtape. These programs occupy two memory pages  $(400_8 = 256_{10} \text{ words})$ .

Several design features are included in the library system. First and perhaps foremost, the system leaves the state of the computer unchanged when it exits. Second, it is capable of calling programs by name from the keyboard and allowing for expansion of the program file stored on the tape. Finally, it conforms to existing system conventions; namely, that all of memory, except the last memory page (7600<sub>8</sub>-7777<sub>8</sub>), is available to the programmer. This convention permits the binary loader (paper tape), and/or future versions of this loader, to reside in memory at all times. The skeleton library tape for the library system contains the following programs:

INDEX Typing this program causes the names of all programs

currently on file to be typed out.

UPDATE Allows the user to add a new program to the files. UPDATE

queries the operator about the program's name, its starting

address, and its location in core memory.

GETSYS Generates a skeleton library tape on a specified DECtape

unit.

DELETE Causes a named file to be deleted from the tape.

Starting with the skeleton library tape, the user can build up a complete file of his active programs and continuously update it.

The last group of programs, a collection of short routines controlled by the contents of the switch register, is called DECTOG. It provides for the recording of timing and mark channels and permits block formats to be recorded for any block length. Patterns may be written in these blocks, then read and checked. Specified areas of tape may be "rocked" for specified periods of time. A given reel of tape may thus be thoroughly checked before it is used for data storage. These programs may also be used for maintenance and check-out purposes.

## CHAPTER 3 CONTROL LOGIC

#### 3-1 INTRODUCTION

Control logic for the Type 552 DECtape Control is explained by reference to pertinent timing diagrams and to DEC engineering drawings BS-D-552-0-3 through BS-D-552-0-8. In this chapter, the engineering drawings will be referenced only by the last number and where applicable a colon and the zone. Circuit locations on the drawings will be referenced by a numeral-letter-numeral symbol; the first numeral designates the last digit of the drawing number, while the following letter-numeral combination designates the location of the circuit on the drawing (see Chapter 6).

Reduced engineering drawings, with applicable symbol conventions, are in Chapter 6. These symbol conventions should be thoroughly understood before proceeding because they are used in the text and timing diagrams as well as in the engineering drawings.

In the text and timing diagrams, the circuit location symbols defined above cross-reference each event of the program with its associated hardware on the engineering drawings. This cross-referencing forms the basis of the discussion in this chapter.

#### 3-2 COMPUTER INTERFACE

The interface between the computer and its DECtape control includes the following:

- a. <u>Decoding pulse amplifiers</u> which generate in/out transfer (IOT) pulses from computer instructions.

- b. <u>Five registers</u> used for computer-DECtape control communications. These registers are the unit, motion, and function registers shown on BS-8; the data buffer (DB) at bottom of BS-6; and the memory address counter (MAC) at the bottom of BS-5.

- c. Status bits for the tape end, timing error, parity or mark error, and select error flip-flops at top of BS-4. The I outputs of the REV and GO flip-flops (8:B4,5) are also available as status levels, but the computer cannot set or clear these two flip-flops directly.

- d. Data flag and data transfer (DT) flag (4:A2,3).

#### 3-2.1 In/Out Control

The control operations initiated by specific computer instructions are illustrated by the flow diagram of Figure 3-1. In this flow diagram, the shapes of the enclosures indicate the following:

Shape Enclosure for

Ellipse True pulses (e.g., pulse amplifier outputs).

Rectangle Gating levels or changes in the state of the flip-flop.

Pair of horizontal lines Delays specified between lines by duration (e.g., 500 nsec)

and condition (e.g., wait for positive overshoot).

As in timing diagrams, events on the flow chart are keyed to their associated hardware by the circuit location symbols.

The 4605 Gated PA (2L01) for the 675 instructions (MMLS, MMLM, and MMLF) is shown on drawing 8:C1. All three instructions pertain to the jam-transfer of disjunct groups of accumulator (AC) bits into the unit, motion, and function registers. Loading the function register (like loading the MAC) clears the AC through a gate (8:C6) and loads the function register through a pulse inverter (PI) (8:B6). The capacitor-diode (C-D) gates below motion register MOTION<sub>1</sub> (8:B6) are permanently disabled by the 10K resistor to -15v; consequently, the PI only affects the three function-register bits. As long as MOTION<sub>1</sub> is set, the 4151 Binary-to-Octal Decoder (8:A7,8) is fed by the function register and generates the seven tape function levels. The read-all, write-all, and write-timing and-mark (WRTM) functions are ORed together to develop the ALL BITS level (4:C2).

The AC — J MOTION pulse generated by the MMLM (6752) instruction transfers AC bits 7 and 8 into MOTION<sub>1</sub> through the C-D gates (8:85,6) and simultaneously triggers 35-msec delay (8:D3). When this delay times out, it triggers the SELECT delay (8:C3) and the turn-around-and-start-acceleration (TA&SA) delay (8:C3); and simultaneously transfers the contents of MOTION<sub>1</sub> into the REV and GO flip-flops (8:B4,5) through their C-D gates. The transfer into GO is unconditioned, but REV is loaded only if GO becomes 1; hence the direction of a prior tape movement is always available to a transport that is commanded to stop. These REV and GO flip-flops directly control the tape motion at the selected transport through the indicator drivers (ID) (8:B4,5); consequently, tape motion is governed by the contents of AC bits 7 and 8, 35 msec after the MMLM instruction.

The MMLS (6751) instruction generates an AC → UNIT pulse (8:C2). The leading edge of this pulse triggers the lower 35-msec delay (8:D2); and 400 nsec later, the trailing edge triggers a PA (8:C1). This PA develops a 1-msec pulse whose trailing edge transfers the contents of AC bits 2-5 into

the unit register. Because of the cascaded trailing-edge triggers, the transfer occurs 1.4 µsec after the computer's IOP 1 pulse. Such a delay is required because PDP-8 accumulator bits may be indeterminate up to 0.5 µsec before IOT 1, and this is insufficient time to enable the C-D gates at the unit register flip-flop. In the NAND gates of the 4112 module (8:C4) the 35-msec delay negates both outputs of UNIT<sub>3</sub>, disabling the 4671 Binary-to-Decimal Decoder (8:B1,2,3). The MMLS (6751) instruction, therefore, deselects the previous transport 35 msec before selecting another. This delay interval allows for all deselected transport relays to drop before picking up relays of the newly selected transport. While the delay enables the new selection, it also triggers SELECT and TA & SA delays (8:C3). The ground return for the 4671 Decoder is connected through a 5-ohm resistor (8:A1). If unit register (8:B1,2,3) is loaded with a code that addresses more than one drive, the decoder draws double (or more) the normal current; hence, the drop across the return resistor is doubled. If the unit register cannot address any drive, no decoder current is drawn and the drop across the return resistor is zero. The two adjacent 1501 Difference Amplifiers (8:A1) sample the drop across the return resistor and assert SINGLE UNIT in response to either select error.

When the SELECT delay (8:C3) times out, it sets the DT flag (4:A3). Unless the function register specifies one of the all-bits functions, the DT flag asserts the interrupt level (4:A1) causing a program interrupt. The TA & SA delay (8:C3) clears the state generator prior to beginning new tape operations. When the delay terminates, its 0 output clears the window register and enables the production of timing pulses. If a null or multiple selection has been made, the TA & SA delay signals the program when it times out by setting the select-error flip-flop through the C-D gate (4:B8). A selection or motion instruction repeated while the select delay is set (i.e., between 35 and 70 msec) causes a timing error through C-D gates (4:B6). All error flip-flops assert the ERROR level (4:B8) which requests a program interrupt (4:A1). A timing error also results if the control sets either flag while it is already 1, indicating that the computer has failed to service a data-break request or a program interrupt.

The 4605 Gated Pulse Amplifier (4:C5) is used for the MMSC (6671), MMCF (6772), and MMRS (6774), instructions. An MMSC (6771) generates a pulse that samples the ERROR at gate (4:A2), and a pulse out at the SKIP line adds 1 to the computer program counter (in addition to the increment that is normally part of each cycle). A clear-flags pulse generated on the MMCF (6772) instruction clears all four error flip-flops through the PI(4:A4), and the DT flag through gate (4:D3). The report-status pulse generated by MMRS (6774) drives the row of gates (4:A-3), setting AC bits that correspond to asserted status levels.

The last three instructions are decoded by the 4605 Gated-Pulse Amplifier (5:D2). The SKIP DT-flag pulse from instruction MMSF (6761) pulses SKIP line (4:A2) when the DT flag is 1. The other two pulses clear and load the MAC and MAC EXT (5:D3). The load pulse generated by MMLC (6764) functions as a trailing-edge trigger for the PA(5:D1); the PA output loads MAC (5:C1), clears AC (8:C6) and loads

MAC EXT (5:D3) from the data-field register in the computer memory-extension control. DECtape controls (designed for use with computers having more than four 4K memory modules) have an additional MAC EXT flip-flop. The 1 outputs of MAC and its extension are made available to the computer through buffers at ground assertion, and specify the address for a data transfer during data-break cycles initiated by this control.

#### 3-2.2 Data Transfers

Full-word 12-bit transfers are made between the memory buffer (MB) and data buffer (DB) shown at the bottom of drawing 6. DB is not available to the program; transfers take place only to or from the memory location specified by MAC in a computer data-break cycle requested by DECtape data flag (DT). The direction of information flow is determined by FUNCTION<sub>0</sub> (5:D7), and is 1 for all write operations. A negative 0 output asserts the DATA IN signal (5:D7) to the computer for move and read operations; data breaks then transfer the information into memory. The data flag asserts the BREAK REQ signal through an inverter (4:A1). MAC has its own increment logic, so that the address-increment request level (4:A1) to the computer is permanently disabled at ground. When the address in MAC and its extension have been transferred to computer memory address and extension registers, the computer returns the ADDRESS ACCEPTED pulse which clears the data flag. Except in the search mode, this pulse also increments MAC through a gate (5:C8) to obtain the address for the next transfer.

DB (6:C1) receives MB 1 outputs (5:D8) asserted at ground; internal inverters generate the corresponding 0 levels to allow a jam-transfer of information. For writing, the MB — J DB pulse is generated by the logic at the lower right of BS-5. During the break cycle, the level (B(1) is asserted from the computer and C-D gate (5:D6) is enabled. Timing pulse T5 (5:D6) from PDP-5 or T2B from PDP-8 generates the MB strobe pulse for the DB through the C-D gate and PA(5:D8). In reading, read/write buffer (RWB) on drawing 6 accepts read amplifier levels at one end of each 4-bit shift segment. Four successive shifts assemble in RWB a full word, which is then transferred to DB as data flag (7:C2) is set. While RWB assembles the next word from tape, the contents of DB are available to memory through the buffers shown above the register.

## 3-3 READ/WRITE LOGIC

The basic circuit for read/write logic, and pertinent waveforms are shown in Figure 3-2. In this figure, the flip-flop below the write amplifier may be a bit of the write buffer (WB) in drawing 6 or it may be the timing-track buffer (TMB) (3:C1) or the mark-track buffer (MKB) (3:B4). For all channels, the hardware is identical with each read/write module, containing a flip-flop and input gates, a write amplifier

LOAD - D

WRITE AMP

FF

Figure 3-2 Read/Write Waveforms

governed by the flip-flop outputs, and a read amplifier. Read inputs are paralleled with the writeamplifier outputs across the head. Hence, the read amplifier responds to signals from both the head and the write amplifier.